在2018年末,三星和台積電推出了具有5至7個(ge) EUV層的7nm晶圓代工邏輯工藝,兩(liang) 家公司在整個(ge) 2019年也都加快了這些工藝的生產(chan) ,現在正在大量生產(chan) 中。進入今年,三星和台積電都在加快具有12至14個(ge) EUV層的5nm晶圓代工邏輯工藝的進度,而英特爾正在研究明年有望基於(yu) EUV的7nm工藝。英特爾的7納米製程密度應與(yu) 三星和台積電的5納米製程相當。

三星還於(yu) 2019年末推出了其1z DRAM工藝,該工藝最初是光學的,但隨後過渡到單個(ge) EUV層。2020年3月下旬,三星宣布已出貨100萬(wan) 個(ge) 基於(yu) EUV的DRAM模塊。三星的下一代DRAM工藝,即所謂的1c代DRAM有望具有4個(ge) EUV層。

顯然,EUV已被公認為(wei) 是領先邏輯和DRAM生產(chan) 關(guan) 鍵層的最佳解決(jue) 方案。

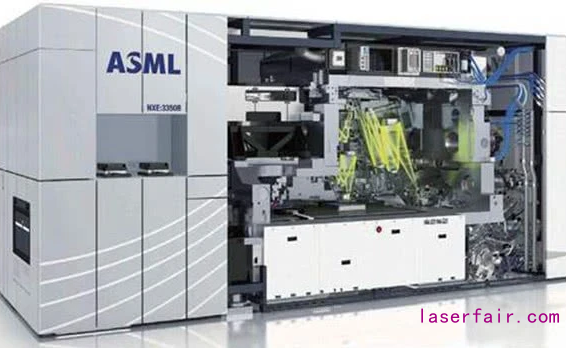

而在今年的SPIE高級光刻會(hui) 議,ASML的Mike Lercel展示了公司EUV的四個(ge) 方麵:

1、當前的生產(chan) 是使用0.33NA係統完成的,ASML給出了這些係統的當前狀態和路線圖。2、EUV源是係統的關(guan) 鍵組成部分,並描述了新的改進源的詳細信息。3、生產(chan) 0.5NA係統以提高分辨率和生產(chan) 率的工作狀況。4、ASML收購了HMI,並將繼續開發其多光束– Ebeam晶圓檢測技術。

0.33NA係統

關(guan) 於(yu) 這方麵,ASML的總結如下圖所示:

截至2019年底,ASML已交付了53套係統,並且在該領域已曝光超過1000萬(wan) 片晶圓。圖2展示了按季度分列的發貨係統和曝光的晶圓。

圖2

圖2的一個(ge) 特別令人印象深刻的方麵是背景照片,該照片顯示了在未公開客戶現場安裝的成排的EUV係統。該領域的當前係統是NXE:3400B,該係統現在已經證明一周平均每天> 1,900 wpd,最好的一天超過2,700 wpd。圖3說明,平均可用性現在已達到85%,而係統的前10%則為(wei) 90%。90%一直是3400B係統的目標,ASML繼續努力將3400B係統的可用性提高到90%左右。

圖3

ASML現在已經開始交付下一代係統NXE:3400C。NXE:3400C具有改進的光學性能和機械吞吐量,與(yu) 3500B相比,新機器在在20mJ/cm 下可獲得每小時160片晶圓(wph)的效率,在30mJ/cm2下則能獲得135 wph的效率,那就意味著吞吐量提高了約20%。

在3400B,設備的指定為(wei) 20mJ/cm 用於(yu) 生產(chan) 量,而30mJ/cm 則是因為(wei) 需要隨著特征尺寸的縮小而增加。作者注意到,我相信即使對於(yu) 7nm晶圓代工邏輯,目前的數字仍高於(yu) 30mJ/cm 。

3600C對係統進行了幾處改進,以提高可用性。據相關(guan) 數字透露,他們(men) 的目標是將其可用性提高到95%,這將與(yu) DUV係統所達到的可用性相同。這些改進將在源代碼的論文中進一步討論。

ASML預計在2021年中期以30mJ/cm 交付具有160 wph吞吐量的NXE:3600D,並且更長期地計劃推出以30mJ/cm 達到220wph的係統。吞吐量不斷提高的關(guan) 鍵是更高的光源功率(請參見EUV光源部分)和更快的機械處理。在不斷提高dose準確性,覆蓋(overlay),CD均勻性(uniformity )和聚焦均勻性(uniformity )的同時,實現了這些吞吐率的提高。

EUV光源3400B係統上最大的可用性損失原因是液滴產(chan) 生器和收集器反射鏡,見圖5。

圖5

3400C係統通過自動重新裝錫發生器,快速更換墨滴噴嘴(droplet nozzle)和方便檢修門以快速更換收集器鏡(mirror swaps)來解決(jue) 這些問題。

聚光鏡的壽命也在不斷提高,而功率也在增加。

這些改進的最終結果是在現場將3400C係統的正常運行時間目標定為(wei) 95%。為(wei) 了實現吞吐量的不斷提高,ASML將繼續提高電源功率。圖8說明了電源功率的趨勢。請注意,從(cong) 研究到大批量生產(chan) 的時間大約為(wei) 2年,因此我們(men) 可能會(hui) 在2022年左右看到500瓦的電源(目前的電源大約為(wei) 250瓦)。

0.5NA係統曝光係統的分辨率與(yu) NA成反比。隨著關(guan) 鍵尺寸的縮小,0.33NA EUV係統將需要multi-patterning才能印刷出最小的特征。高NA係統的目標是使0.33NA係統的覆蓋率和生產(chan) 率匹配,同時使單程光刻技術擴展到更小的特征。0.5NA係統的光學係統是變形(anamorphic)的,即在一個(ge) 方向上的放大倍數為(wei) 4x,在正交方向上的放大倍數為(wei) 8y。這導致場大小是具有相同標線片大小的4x/4y係統的場大小的1/2。為(wei) 了實現高生產(chan) 率目標,掩模台的加速度是0.33NA係統的4倍,晶圓台的加速度是0.33NA係統的2倍。

快速階段中傳(chuan) 輸的改進導致在相同吞吐量下,0.55NA係統比0.33NA係統的吞吐量有所提高。這裏應該注意,為(wei) 0.55NA係統開發的一些高速sateg技術正在0.33NA係統上實現,以進一步提高這些係統的吞吐量。

目前,ASML正在實現晶圓和掩模台加速並最終確定架構。這與(yu) 0.33NA係統的主要區別在於(yu) 新的光學係統和更快的stage,盡管更快的stage技術再次用於(yu) 0.33NA係統。0.55NA係統還需要更好的對準和水平度。ASML當前正在測試特定配置,以確定高加速度下的顆粒生成,並開始收集一些第一批傳(chuan) 感器數據。ASML還在世界各地的各種設施中構建0.55NA係統的基礎架構。

1、康涅狄格州的ASML Wilton負責標線階段。

2、係統將在荷蘭(lan) Veldhoven的ASML總部組裝。

3、德國Oberkochen的Ziess負責光學製造。

4、光源是加利福尼亞(ya) 聖地亞(ya) 哥的ASML負責。

目前公司有4個(ge) 係統在訂購中,預計將在2022/2023年的時間範圍內(nei) 可用。

多光束EBeam

ASML收購了HMI,並繼續追求HMI多光束EBeam曝光技術。電子束檢查具有很高的分辨率,但檢查0.1%的芯片大約需要2個(ge) 小時,非常緩慢。

多光束方法利用3x3陣列中的9個(ge) 光束同時掃描。圖11說明了基本工具概念。

現在,ASML已證明光束之間的串擾小於(yu) 2%,並且他們(men) 正在利用DUV曝光工具中的stage技術來提高多光束係統的通量。他們(men) 的目標是將吞吐量提高5-6倍,並且長期使用25光束係統。毫無疑問,EUV現在是用於(yu) 領先工藝的關(guan) 鍵光刻的首選解決(jue) 方案。ASML繼續展示當前的0.33NA生成係統和下一代0.55NA係統的開發進展。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們