3 總體(ti) 設計

3.1 屏體(ti) 接口模塊

屏體(ti) 接口包括屏體(ti) 接口頭文件、屏幕緩衝(chong) 區的定義(yi) 、屏體(ti) 接口初始化、刷新定時器中斷服務程序和SPI中斷服務程序幾個(ge) 部分。

屏體(ti) 接口的頭文件screen.h 應該使屏幕緩衝(chong) 區對其他應用可見, 並提供屏體(ti) 初始化函數。具體(ti) 定義(yi) 如下:

#ifndef _SCREEN_H_

#define _SCREEN_H_

#include “inc\board.h”

extern u8 xdata SCR_BUF[16][16];

void screen_init(void);

#endif

這樣就把屏幕緩衝(chong) 區的結構暴露給應用, 但應用不必關(guan) 心具體(ti) 的屏幕刷新操作。

具體(ti) 屏體(ti) 接口的實現集中在一個(ge) 文件screen.c 中定義(yi) 。具體(ti) 如下:

首先是屏幕緩衝(chong) 區定義(yi) :

u8 xdata SCR_BUF[16][16]_at_0x0000;//~0x00ff 256Bytes其次是當前顯示行和輸出列變量定義(yi) , 屬於(yu) 靜態變量, 應用程序不可見。

static u8 data row,col;

然後是屏幕初始化, 包括刷新定時器0 的初始化、SPI 的初始化、鎖存bLatch 信號的初始化、屏幕緩衝(chong) 區的初始清零以及定時器和SPI 中斷的優(you) 先權和使能位的初始化代碼略。

SPI 和定時器0 的中斷服務程序是屏體(ti) 接口的關(guan) 鍵。

定時器0 的中斷服務程序首先進行掃描行增量取模運算,並將掃描行輸出。然後依據掃描行取出屏幕緩衝(chong) 區對應行的第一個(ge) 字節發送到SPI 端口。同時列增量。

void display_ONe_screen(void)interrupt 1 using 3{

row = (++row)&0x0f;

P0 = (P0 & 0xf0)|((~row)& 0xf);

col = 0;SPDAT = ~SCR_BUF[row][col++];

}

這樣編寫(xie) 的屏體(ti) 驅動, 應用隻要在初始化屏體(ti) 後,向屏幕緩衝(chong) 區中寫(xie) 入要顯示的數據即可, 而不必關(guan) 心屏幕顯示的細節。

3.2 UART 接口

UART 接口負責與(yu) 上位機的數據收發, 盡管發送可以同步進行, 但接收必須異步進行。因而UART 接口的核心仍然應該是一個(ge) 中斷服務程序。

UART 接口的頭文件uart.h 隱藏了接收緩衝(chong) 區的信息, 用戶可調用的函數隻有初始化、發送和接收。

#ifndef _UART_H_

#define _UART_H_

void uart_init(void);

void uart_put_c(u8 ch);

u8 uart_get_c(u8 *);

#endif

UART 的接口實現首先定義(yi) 一個(ge) 接收緩衝(chong) FIFO, 以及對FIFO 的讀下標uart_rd 和寫(xie) 下標uart_wr, 他們(men) 都是文件內(nei) 可見的靜態變量:

static u8 xdata uart_buf[64];

static u8 uart_rd,uart_wr;

bit fSend

UART 的初始化包括進行FIFO 的初始化和UART格式、波特率、中斷的初始化。代碼略。

UART 的ISR 主要是服務於(yu) 接收, 無條件地將數據裝入FIFO, 並調整寫(xie) 入指針。

static void uart_isr(void)interrupt 4 using 1{

if(RI){RI = 0;

uart_buf[uart_wr++] = SBUF;

uart_wr &= 0x0f;

}

}

提供給用戶的發送程序首先檢測發送結束標記, 如果為(wei) 0, 表示上次發送尚未結束, 直接返回錯誤信息1。

否則將要發送的信息發送並清零發送結束標記。這樣設計的發送程序, 其目的是將發送等待不限製在接口底層, 而是給上層一個(ge) 決(jue) 定是否等待發送結束的機會(hui) 。

u8 uart_put_c(u8 ch){

if(! TI)return 1;

TI = 0;SBUF = ch; return 0;

}

同樣, 接收程序也給上層一個(ge) 選擇等待的機會(hui) 。接收函數首先判斷接收FIFO 是否為(wei) 空, 如果為(wei) 空或輸入指針參數錯誤, 則直接返回錯誤, 否則才從(cong) FIFO 中讀取數據並將數據存儲(chu) 到指針指向的地址, 然後返回成功。

u8 uart_get_c(u8 *ch){

u8 i;

if(! ch)return 1;

if((i = (uart_rd+1)&0x0f) == uart_wr)return 1;

uart_rd = i; *ch = uart_buf[i];return 0;

}

3.3 閃存接口

閃存的存取有特殊的時序, 閃存的內(nei) 部結構也和具體(ti) 應用要求有很大的不同。因此閃存的接口需要仔細設計。

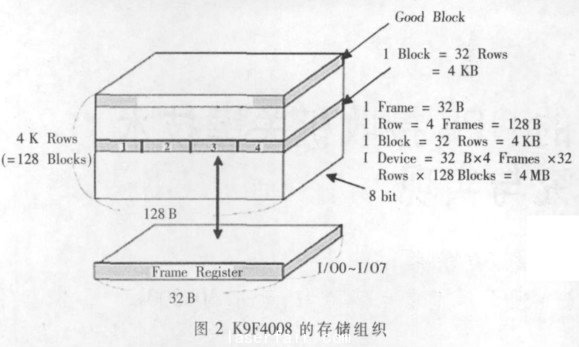

K9F4008 閃存芯片的存儲(chu) 結構組織如圖2所示。

K9F4008 閃存的存儲(chu) 以塊為(wei) 單位, 每個(ge) 芯片共有128 塊。每塊有32 行, 每行有4 個(ge) 幀, 每幀含有32 B.全部芯片為(wei) 512 KB。

閃存接口提供的閃存初始化函數中就包括對這樣情況的處理。初始化函數要從(cong) 閃存的第一個(ge) 塊中讀出一個(ge) 塊映射表, 該表下標是邏輯扇區, 表內(nei) 每項存儲(chu) 的是該邏輯扇區對應的物理塊編號。初始化函數在必要時對閃存進行讀寫(xie) 校驗, 然後將壞塊從(cong) 表中刪除。再尋找新的良好塊, 將其編號填入到對應邏輯扇區的表項中。這樣對應用來說, 隻見到連續的扇區編號, 而不知道扇區究竟對應到那個(ge) 塊。

閃存的接口頭文件Flash.h 如下:

#ifndef _K9F4008_H_

#define _K9F4008_H_

void read_log_page(u8 sector,u8 page,u8 xdata *buf);

u8 prog_log_page(u8 sector,u8 page,u8 xdata *buf);

void erase_log_blk(u8 sector);

bit flash_init(void);

#endif

實現閃存的接口, 首先就是依據說明書(shu) 的時序定義(yi) 閃存的基本操作。這裏是以宏定義(yi) 實現基本操作的。

#define W_CMD(cmd_)\

bCLE=1; bWE=0; P2=(cmd_); bWE=1; bCLE=0

#define W_ADDR(addr1_,addr2_,addr3_)\

bALE=1; bWE=0; P2=(addr1_); bWE=1; \

bWE=0; P2=(addr2_); bWE=1; \

bWE=0; P2=(addr3_); bWE=1; \

bALE=0

#define W_DAT(dat_) bWE=0; P2=(dat_); bWE=1

#define wait_RB while(! bRB)

#define l2p(x_) fat_tbl[(x_)]

3.4 EEPROM

內(nei) 部集成的EEPROM 是與(yu) 程序空間分開的, 利用ISP/IAP 技術可將內(nei) 部DATAFLASH 當EEPROM,擦寫(xie) 次數10 萬(wan) 次以上。EEPROM 可分為(wei) 若幹個(ge) 扇區, 每個(ge) 扇區包含512 B.使用時, 建議同一次修改的數據放在同一個(ge) 扇區, 不是同一次修改的數據放在不同的扇區, 不一定要用滿。數據存儲(chu) 器的擦除操作是按扇區進行的。

sfr IAP_DATA = 0xC2; //Flash data register

sfr IAP_ADDRH = 0xC3; //Flash address HIGH

sfr IAP_ADDRL = 0xC4; //Flash address LOW

sfr IAP_CMD = 0xC5; //Flash command register

sfr IAP_TRIG = 0xC6; //Flash command trigger

sfr IAP_CONTR = 0xC7; //Flash control register

根據使用說明對EEPROM 的寄存器進行定義(yi) 。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們