一、引言

隨著光電子技術的飛速發展,激光雕刻技術應用範圍越來越廣泛,雕刻精度要求越來越高。體(ti) 現激光材料加工的發展水平有三個(ge) 方麵的因素:第一是激光器技術,即應用於(yu) 激光材料加工的激光器件技術;第二是激光設備加工的機械、控製係統等,即激光加工設備;第三是激光加工工藝水平。因為(wei) 激光器技術已經是很成熟的技術,所以能否對激光設備進行有效的控製以及激光的加工工藝水平成為(wei) 激光雕刻技術應用的瓶頸。

目前,國內(nei) 專(zhuan) 門生產(chan) 激光雕刻設備的廠家很多,他們(men) 競爭(zheng) 已由激光器技術轉向對激光設備和加工工藝的有效控製,能否有效解決(jue) 如下問題,三維圖形多軸聯動、高速激光掃描和快速推進引起的振動、掃描幅麵大小和掃描精度、激光的同步掃描和往複掃描錯位、複雜算法和規則圖形插補問題等,已經成為(wei) 競爭(zheng) 的關(guan) 鍵。

二、基於(yu) DSP和FPGA的設計

針對上述各種問題,結合多年運動控製的經驗,我們(men) 設計了基於(yu) 資源豐(feng) 富的FPGA和功能強大的DSP的運動控製板卡——MPC03,在激光雕刻調試中,成功的解決(jue) 了上述各種問題。

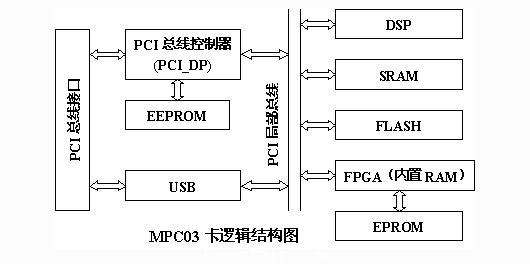

1.MPC03卡電路設計在MPC03卡中主要有DSP、FPGA兩(liang) 個(ge) 功能芯片,在DSP周圍擴展了多個(ge) FLASH和SRAM來存儲(chu) 程序和數據,每兩(liang) 個(ge) FLASH和SRAM可以共用一個(ge) 片選信號CS,組成高低雙字32位數據總線進行讀寫(xie) ,可以提高DSP與(yu) MEMORY的通信速度,同時為(wei) FPGA配置了一個(ge) EPROM來存儲(chu) 下載的程序。連接DSP局部總線和PCI接口的芯片是PCI總線控製器(PCI橋),它包含了一個(ge) 128KBit的雙口共享存儲(chu) 器,來實現DSP局部總線和PCI係統總線的數據交換,另外為(wei) 其配置了一個(ge) EEPROM來存儲(chu) 數據,同時本卡順應了即插即用接口設計趨勢,擴展了USB接口。本文提到的DSP和FPGA都是低能耗、低電壓操作,I/O信號電壓是3.3V,而內(nei) 核電壓是1.8V,所以配置了能同時輸出3.3V和1.8V兩(liang) 種電壓的電壓調整器。請參照MPC03卡邏輯結構圖。

FPGA資源充足,性價(jia) 比高,能現場重複多次編程,可以針對不同的小批量客戶的具體(ti) 要求,靈活地修改設計。DSP具有高速浮點運算的能力,對S-曲線運動過程中的數據和一些插補算法,進行運算處理,擺脫對PC機的依賴,並把處理的數據實時地與(yu) FPGA通信。PCI接口使用比較普遍,總線資源豐(feng) 富,通訊速度塊、尋址空間大。USB接口可實現脫機工作,不必為(wei) 每塊板卡配置一台PC機,工業(ye) 現場使用方便,成本低,符合時代發展趨勢。

2、各種功能的實現

由於(yu) 本方案確定得當,在每一片FPGA芯片上可以實現四軸功能完全相同但彼此相互獨立的操作,能夠實現多軸聯動,對於(yu) 平麵圖形和三維圖形處理,可以采用兩(liang) 軸和三軸聯動。

在掃描中,基於(yu) 開辟的RAM區,采用位圖象素控製,不僅(jin) 解決(jue) 了大幅麵圖形的處理,而且實現了同步掃描中,提高了掃描精度,保證了圖像的雕刻質量。

⑴ 采用S曲線實現平穩高速運動和快速推進

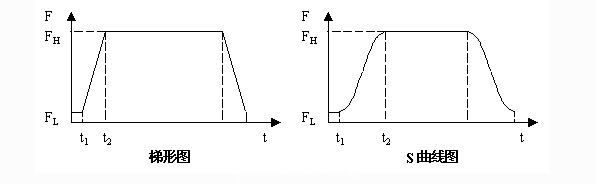

在高速往返運動和快速行推進過程中,如果不加技術處理,如梯形圖所示,在加速度很大的高速運動過程中,就會(hui) 出現振動、衝(chong) 擊,圖形就會(hui) 出現不規則的錯位,嚴(yan) 重時就會(hui) 出現類似波紋狀的變形。如果將加速度減小,則增速時間(t2-t1)就很大,由於(yu) 加工區在高速段(FH勻速段),這樣就造成有效加工幅麵減小。為(wei) 了解決(jue) 這個(ge) 問題,在變速運動中采用S曲線,可以使運動在很短的時間裏,由低速向高速或由高速向低速平緩地過渡。經過現場反複的實驗,在同一設備上,可以大大的提高工作效率和圖形的加工質量。

⑵ 利用位圖象素控製,保證同步掃描和掃描精度

為(wei) 了存儲(chu) 大量的掃描數據和達到同步掃描的目的,我們(men) 巧妙地利用了FPGA內(nei) 置的2MBit塊RAM資源來存儲(chu) 每行的圖象數據。在本設計中,我們(men) 開辟了9根地址線尋址的32Bit數據總線接口的RAM區,即16KBit。如果每個(ge) 掃描象素為(wei) 0.1mm,按最高的掃描精度,則理論上掃描幅麵可以達到1.6m。掃描從(cong) 低位地址向高位地址,從(cong) 每行的低位向高位依次進行。每個(ge) 掃描脈衝(chong) ,步進電機驅動激光頭前進一步,同時從(cong) RAM區中讀取一個(ge) 圖形數據,並根據讀取數據的‘1’或‘0’的狀態決(jue) 定是否開關(guan) 光。因為(wei) DSP每次向FPGA的RAM區寫(xie) 入一行圖形數據512×32Bit,所以在對這些16KBit數據處理期間,DSP不需再向FPGA寫(xie) 數據。不僅(jin) 大大提高了激光設備的工作效率,而且也保證了掃描的同步性,對於(yu) 往複掃描出現的整體(ti) 錯位,為(wei) 在軟件上進行反向補償(chang) 也提供了可行性。

在同步掃描時,為(wei) 了提高掃描精度,改善圖像質量,我們(men) 增加了8位激光控製寄存器LCR,通過設置LCR的大小(0~255),來達到提高掃描精度的目的,請看如下分析:

位圖像素控製激光開關(guan) 存在的問題

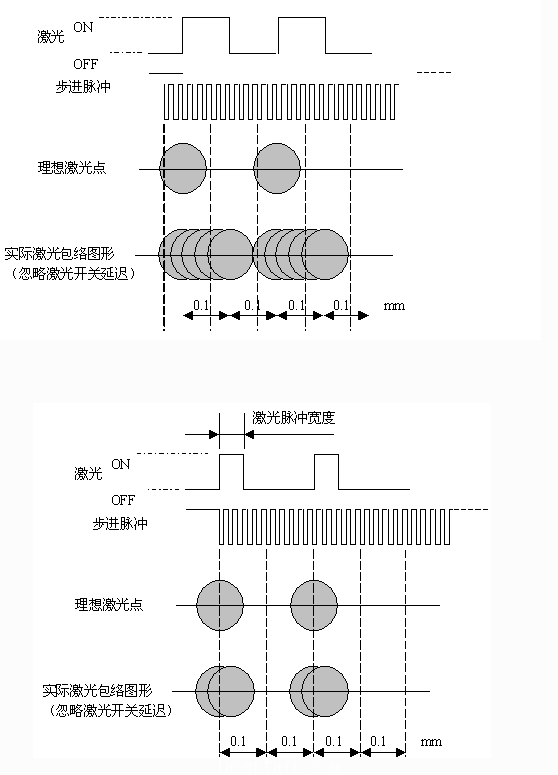

舉(ju) 例分析:假設位圖數據為(wei) 1010,光斑直徑為(wei) Ф0.1mm,單像素脈衝(chong) 數5,則步進脈衝(chong) 和激光掃描如下:

從(cong) 上麵圖形分析可以看出:如果完全根據位圖像素控製,激光脈衝(chong) 寬度為(wei) 單像素脈衝(chong) 數決(jue) 定的寬度;由於(yu) 激光光斑直徑的存在,理論上在開激光點的位置會(hui) 出現“過切”現象,即像素為(wei) ‘1’的點會(hui) 吃掉下一個(ge) 像素為(wei) ‘0’的點。

激光開、關(guan) 延遲的影響:

1.如果激光開延遲、關(guan) 延遲相等,實際雕刻的圖形將平移;

2.如果激光開延遲>關(guan) 延遲(開光慢、關(guan) 光快),“過切”會(hui) 減小;

3.如果激光開延遲<關(guan) 延遲(開光快、關(guan) 光慢),“過切”會(hui) 增大;

激光脈衝(chong) 寬度的控製

為(wei) 了減小或消除以上“過切”現象,在位圖像素為(wei) ‘1’時,應發出一個(ge) 盡可能短的激光脈衝(chong) 。這個(ge) 激光脈衝(chong) 寬度由激光驅動電源和激光管的開、關(guan) 特性決(jue) 定。但目前能夠準確給出激光開關(guan) 延遲數據的開發者還不多,可以采用試驗的方法確定激光脈衝(chong) 寬度。參照上圖:在像素為(wei) ‘1’的第一個(ge) 步進脈衝(chong) 下降沿觸發激光ON,利用計數器延時TL(由激光控製寄存器LCR的低8位設定)後,將激光關(guan) 斷(OFF)。這樣激光脈衝(chong) 寬度就可以調節,而不是單像素脈衝(chong) 數的寬度。這樣,通過控製激光脈衝(chong) 寬度,在像素為(wei) ‘1’時發出一個(ge) 激光點(而不是一個(ge) 線段),就可以減小上述的‘過切’現象,提高激光雕刻質量。

3、係統的抗幹擾措施

幹擾是工業(ye) 現場和實際應用中不可避免的現象,係統的抗幹擾性能是係統可靠性的重要標誌。印刷電路板是器件、信號線、電源線的高度集合體(ti) ,它設計的好壞對抗幹擾能力影響很大。在本設計中主要采用了以下抗幹擾措施:

⑴ 數、模電路分開:在內(nei) 部電路和外部機械輸入信號中間采用普通光耦或高速光耦進行隔離,將它們(men) 的電源和地線分開。

⑵ 配置去耦電容:在關(guan) 鍵地方配置去耦電容,如電源輸入端接0.1~47μF貼片電容,慮除不同頻率段的幹擾,每個(ge) 元器件的電源和地端都配置0.1μF貼片電容等。

⑶ 配置數字濾波器:對於(yu) FPGA芯片的幾個(ge) 信號,複位、報警、回零等,能引起係統複位或停止,為(wei) 了增加係統可靠性,要加數字濾波器,在此可以用軟件實現,用VHDL語言使這幾個(ge) 信號經過幾級D觸發器(級數視情況而定),再對各級信號進行邏輯與(yu) 或邏輯或。三、結束語

隨著光電子技術和大規模集成電路的不斷發展,激光雕刻必將獲得更為(wei) 廣泛的應用,進而推動DSP和FPGA在相關(guan) 領域的應用和發展。在可以預見的將來,DSP技術和FPGA必將在航天、通信、激光雕刻等諸多領域中獲得更為(wei) 廣泛的應用,進而推動著這些技術的進一步發展。#p#分頁標題#e#

參考文獻:

① DSP實用技術 蘇 濤 等編 西安電子科技大學出版社

② 可編程器件應用導論 曾繁泰 等編 清華大學出版社

③ CPLD/FPGA的開發與(yu) 應用 許誌軍(jun) 等編 電子工業(ye) 出版社

④ PCI係統結構 劉 暉 等譯 電子工業(ye) 出版社

⑤ 現代微機原理與(yu) 接口技術 楊全勝 等編 電子工業(ye) 出版社

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們