整個(ge) 電子行業(ye) 對速度和性能的不懈追求,正不斷改變著高端示波器的標準。雖然在評估示波器時,帶寬曾經是客戶和銷售商關(guan) 注的“關(guan) 鍵指標”,但捕獲和分析當今最快串行和光信號所需要的精確度(即測量精確度和信號完整性),已經成為(wei) 當前最重要的因素。

那麽(me) ,什麽(me) 是測量精確度?帶寬是一種用來比較一台儀(yi) 器與(yu) 另一台儀(yi) 器差別的簡單方式。具有最高帶寬的那台一定是最好的,對吧?可以肯定的是,帶寬非常重要,對於(yu) 高速應用而言,高帶寬是必需的要素。不過,示波器的真正目的,是要盡可能準確地反映出感興(xing) 趣的信號。這實現起來非常複雜,涉及到儀(yi) 器的基本設計、探頭架構和連接配件,以及帶寬之外的參數(包括上升時間、采樣率和抖動本底噪聲)。

當選擇示波器時,工程師應評估的關(guan) 鍵參數概述如表1所示。

市場驅動因素:更好的信號完整性

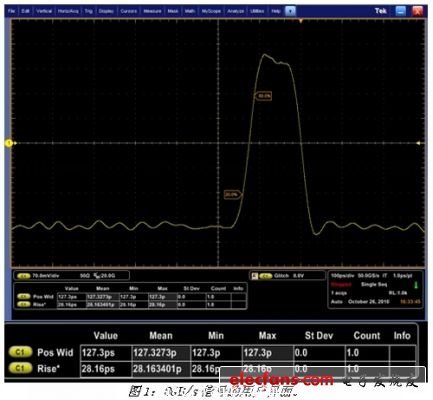

高速信號很容易產(chan) 生信號完整性問題,因為(wei) 它們(men) 涉及到極快的邊沿和極窄的單位時間間隔或位時間。隨著通信鏈路數據速率的增加,將發生兩(liang) 件事:用戶界麵(UI)縮小及信號的上升時間縮短。例如,將5Gb/s脈衝(chong) 與(yu) 8Gb/s脈衝(chong) 進行比較可得,位寬將從(cong) 200ps下降到125ps。這使得設計的裕量或誤差預算降低了38%。此外,這也使接收機的工作更加困難,因為(wei) 它試圖以更小的裕量和非常快的數據速率將1和0進行區分。同時,上升時間也從(cong) 約30ps減少到剛好超過28ps。8GB/s信號如圖1所示。

使問題複雜化的事實是,當傳(chuan) 輸信號進入接收機時,可能產(chan) 生多個(ge) 信號的完整性問題。這些信號的完整性問題可能包括:當此信號流經電路板或從(cong) 矽裸片進入封裝引腳再進入電路板時產(chan) 生的信號衰減。通道內(nei) 的信號衰減是一個(ge) 非常嚴(yan) 重的問題,必須予以解決(jue) 。PCB材料(如FR-4)內(nei) 的信號損失隨路徑長度的增加及數據速率的提高而增大。由於(yu) 信號幅度縮小,噪聲和反射正成為(wei) 一個(ge) 更大的影響因素。客戶需要在接收機中采用去嵌入策略,以打開閉合的眼圖。

隨著第三代串行數據標準的出現,8~10Gb/s正逐漸成為(wei) 行業(ye) 標準。在光通信市場中,隨著以太網發展到4×25G(100GbE),設計人員需要能夠使用高達32Gb/s的比特率對信號進行測試。同時,高速FPGA和寬帶射頻也推動了極限值的擴大。泰克公司的DPO/DSA73304D能夠為(wei) 這些高端應用提供業(ye) 界最精確的測量性能。

技術平台與(yu) 突破

為(wei) 提供業(ye) 界領先的DPO/DSA73304D示波器性能,泰克采用了IBM的8HP鍺化矽技術。這是一種130納米鍺化矽雙極互補金屬氧化物半導體(ti) (BiCMOS)工藝,利用200GHz的FT轉換速度提供了兩(liang) 倍上一代產(chan) 品的性能。

鍺化矽(SiGe)技術利用可靠性高且成熟的製造工藝,提供了能與(yu) 特殊材料(如磷化銦(InP)和砷化镓(GaAs))性能相媲美的性能水平。與(yu) 其它方案不同的是,鍺化矽BiCMOS工藝提供了在一塊芯片上同時製備高速雙極型晶體(ti) 管和標準CMOS的途徑,從(cong) 而使一係列同時具備高集成度和傑出性能的電路成為(wei) 可能。

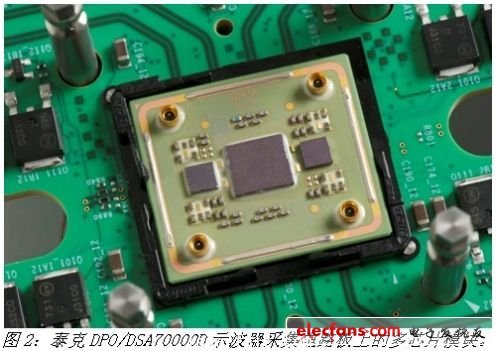

圖2所示的器件是采用SiGe BiCMOS的DPO/DSA70000D示波器新型33GHz、100GS/s前端。該器件稱為(wei) 多芯片模塊或MCM,包含用於(yu) 兩(liang) 條通道的前置放大器(2塊小裸片)及一塊100GS/s采樣保持集成電路(較大裸片)。泰克通過將前置放大器和采樣/保持功能集成到單一封裝之中來提高通道之間的匹配能力,並減少由其他示波器使用單獨的采樣/保持電路和ADC器件引起的交叉失真。

泰克能夠把更多的功能封裝到同一芯片上,減少了元器件和接口的數量,進而降低了噪聲和定時的不確定度,提高了產(chan) 品性能。

IBM的8HP技術是一種130納米(nm)SiGe雙極互補金屬氧化物半導體(ti) (BiCMOS)工藝,其性能是上一代工藝的2倍。SiGe技術采用了擁有50年曆史的矽行業(ye) 相關(guan) 的高度可靠、成熟的鑄造工藝,而其性能水平相當於(yu) 特殊材料的性能,如磷化銦(InP)和砷化镓(GaAs)。與(yu) 替代材料不同,SiGe BiCMOS可以接入到與(yu) 標準CMOS相同的晶粒上的高速雙極型晶體(ti) 管,這實現了一種既有優(you) 異性能、又有大規模集成能力的電路。

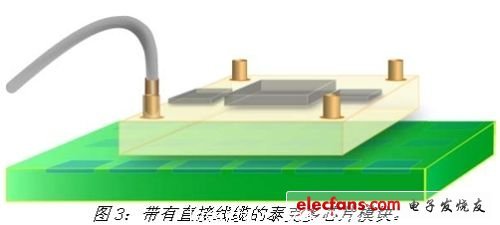

為(wei) 保證最高階測量級信號的完整性,從(cong) DPO/DSA70000D探頭接口輸入的電信號使用高性能電纜直接傳(chuan) 送到多芯片模塊(圖3)。通過利用這種前所未有的方式,隻有在采樣保持芯片捕獲測試信號後,測試信號才接觸示波器采集電路的PCB,從(cong) 而實現了100GS/s的采樣率和行業(ye) 領先的噪聲性能。

我們(men) 為(wei) 此種前端設計提供的另一項創新是較大的偏移範圍和終端性能。該性能通過前置放大器芯片上的分離路徑輸入結構和多芯片模塊上的AC接地端接電阻器來實現,可以更加輕鬆地對大型直流偏置或直流偏置終端信號作出準確的測量。

由於(yu) 實現了向8HP技術的轉變,DPO/DSA73304D示波器可以提供卓越的信號采集性能和分析能力。它幫助設計人員利用全部四個(ge) 通道前所未有的捕獲功能捕捉實時信號,並且利用業(ye) 界最高的波形捕獲能力來捕捉更多的信號細節。利用一套工具集(為(wei) 提供更快的設計和一致性測試而設計)實現高速串行數據信號的自動設置、捕獲及分析。

示波器主要性能包括:雙通道高達33GHz和100GS/s,四通道高達23GHz和50GS/s;小於(yu) 9ps的上升時間(通常為(wei) 20/80);低於(yu) 0.56%的垂直噪聲,≥5.5的有效位數;30多個(ge) 可定製特殊應用軟件分析包。

示波器性能考慮

由於(yu) 示波器是設計方麵(尤其是信號完整性方麵)至關(guan) 重要的工具,設計人員應熟悉示波器的指標及它們(men) 影響測量的方式。讓我們(men) 觀察一下最重要的三大因素:上升時間、采樣率和帶寬,從(cong) 而對它們(men) 進行更深入的了解。

上升時間:示波器的上升時間越快,測量到的上升時間就越準確。但是,當示波器的帶寬或上升時間和信號的上升時間彼此更接近時,會(hui) 怎樣呢?有人曾用經驗法則(如:0.35/上升時間)來計算所需的示波器帶寬,但這種經驗法則隻適用於(yu) 某些示波器的前端設計,並且通常不適用於(yu) 當今為(wei) 高速串行數據速率和伴隨的快速上升時間而優(you) 化的前端設計。

應當注意的是,具有相同帶寬性能的兩(liang) 台示波器可以具有完全不同的上升時間、幅度和相位響應。所以,僅(jin) 了解示波器的帶寬無法可靠地揭示出其測量性能。此外,通過計算確定的上升時間可能也不準確。了解示波器上升和下降時間響應的最可靠方法是,使用一個(ge) 比被測示波器信號快得多的理想的階躍信號對其進行測量。

在使用DPO/DSA73304D的情況下,使用這種方法確定出9ps的上升時間。但是,信號速度可以被測量的意思是什麽(me) 呢?根據正確的經驗法則,信號上升時間與(yu) 示波器上升時間的比值為(wei) 2x或>18ps。事實證明,對於(yu) 當今最快的FPGA設計中使用的28Gb/s的串行解串器(SerDes)而言,這是指定的上升時間。

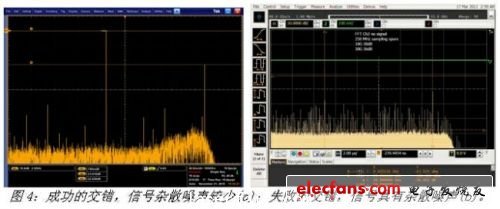

采樣率:因為(wei) 更快的采樣率將帶來更多的波形細節,所以這一因素非常重要。另一方麵,對最快的信號而言,采樣率不足可能導致欠采樣。DPO/DSA73304D提供了一流的采樣率性能。利用交錯技術提供的采樣率性能可將雜散高頻的影響降至最低,該技術采用的是8路采樣/保持方法。參見圖4中的數據,可得出成功和失敗執行的交錯技術的差異。#p#分頁標題#e#

奈奎斯特定理(Nyquist theorem)指出,采樣係統應以輸入信號最高頻率的2倍以上進行采樣。雖然這是最低的起點,但是在任何情況下,采樣率越高,結果越準確。通過使用2.5倍於(yu) 輸入頻率的較高采樣率或更高的采樣率,可以提供更多的感興(xing) 趣信號上的采樣點,且能避免混疊。對於(yu) 極高速信號的表征而言,這將特別重要。

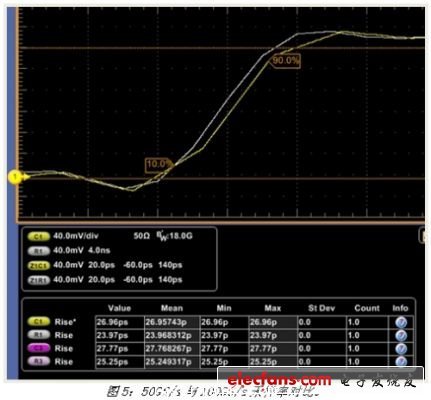

圖5顯示了較高的采樣率值。黃 色跟蹤線(C1)在50GS/s上,而白色跟蹤線(R1)在100GS/s上。過采樣的原因包括:為(wei) 確保信號中已知和未知的高頻部分被捕獲,且沒有混疊;為(wei) 實現卓越的定時分辨率(特別是快速瞬態信號或邊緣上的定時分辨率);作為(wei) 一種減少測量中噪聲的手段,采樣過密會(hui) 減少示波器模數轉換時附帶產(chan) 生的量化噪聲。

帶寬:示波器必須有足夠的帶寬來捕捉高頻部分,以便準確地顯示信號的轉換。但是,當銷售商為(wei) 帶寬需求進行善意提示,推薦5次諧波時,事情在不斷發生變化。邊沿速率(上升/下降時間)的變化並沒有與(yu) 數據速率的變化同步。這意味著,所需的最大帶寬受上升時間的影響更大。例如,目前第三代規格的上升時間在30ps的範圍內(nei) 。隨著速率的不斷提高,這似乎並沒有很大變化,這表明,相對於(yu) 數據速率的信號諧波含量正在下降。

設定垂直量程:除帶寬、采樣率和上升時間外,對高性能示波器來說,觀察當前高頻信令中常見的低壓信令非常重要。在這一領域中,DPO/DSA70000D係列提供了無可比擬的靈活設定垂直量程的能力,是唯一提供可變端接電壓(Vterm)的高性能示波器。在傳(chuan) 統上,示波器輸入一直是接地的,而被測信號通常沒有參考地電平。多種現代應用(包括DC耦合信號應用)現在要求具有正或負的端接電壓才能運行和檢測。把這些高速信號引到大地至少會(hui) 損害測量結果,要求專(zhuan) 用夾具電平移位和/或衰減信號,則可能會(hui) 損壞被測器件(DUT)。

過去,調節測量係統的端接電壓需要采用專(zhuan) 用探頭或定製衰減器網絡,這引入了額外的測量噪聲,需要額外的成本。DPO/DSA70000D係列為(wei) DUT提供了高達±3.4V的可變Vterm,並在前端MCM采用了分路電路設計,支持較大的偏置範圍。

用戶可以調節示波器、鏡像DUT的條件和特點,在其最終運行的類似環境中測量高速信號,而沒有引入衰減或可能使信號失真的定製電路。

隨著現代高速信號的電壓範圍下降,工程師還需要具有廣闊靈活的測量視角。DPO/DSA70000D係列與(yu) Vterm功能相結合,提供了±3.4V的擴展偏置範圍。這不僅(jin) 是一種放大功能,還可以在全部動態範圍查看和測量可變電壓。通過結合使用Vterm和偏置,把示波器的參考點中心放在DUT工作範圍的參考點上,可以使可用的動態範圍達到最大,並使測量係統的噪聲達到最小。

精確性和強大的捕獲能力

高性能技術應用正在推動現代測試設備的發展。矽檢定、串行數據一致性測試、光學調製分析、雙倍數據速率(DDR)存儲(chu) 器和寬帶RF檢驗等任務,不僅(jin) 要求具有傑出的帶寬、采樣率和信號保真度,還要求具有巨大的靈活性,來調節示波器的測量條件和視角。

泰克DPO/DSA70000D係列示波器在實時示波器中同時實現了行業(ye) 領先的信號完整性和定時精度,使用戶能夠更準確的、以更高的信心來完成設計,設計人員能夠:利用業(ye) 界最精準的采集係統,發現感興(xing) 趣的重要信號。此類采集係統的特征是采用了在示波器和探頭中使用的可靠鍺化矽技術;使用市場上最廣泛的觸發係統,捕獲高速信號評估所需的精確的信號事件;利用高采樣率搜尋記錄,以確定關(guan) 鍵事件/誤差,用於(yu) 係統驗證;評估要求正或負端接電壓的DC耦合信號,而不會(hui) 把信號牽引到地或損壞被測器件;利用30GHz以上的示波器中最高的信噪比,快速分析關(guan) 鍵測量結果。它能夠提供高靈敏度、低噪聲的測量結果,從(cong) 而為(wei) 進行精確的高速光學、能量和串行數據測量定性分析提供依據。

尖端軟件與(yu) DPO/DSA70000係列平台上的用戶界麵工具相結合,為(wei) 複雜測量方案(包括調試/分析)提供了最短的快速響應時間。DPO/DSA73304D通過與(yu) 高帶寬、高采樣率和快速上升時間相結合,可以為(wei) 現今最高的信號完整性測量需求而進行特別的量身定做。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們