視頻圖像信號處理(ISP)從(cong) 模擬信號時代發展而來,已經經曆了很長一段時期。今天,數字信號處理實現了可以在位級進行圖像數據處理,為(wei) 圖像質量提供了前所未有的控製。數字信號處理顯然不等同於(yu) 數字信號處理器或DSP.雖然DSP已經被廣泛用於(yu) 視頻圖像信號處理的數字領域,ISP可以由各種處理器件實現,如DSP、ASIC、ASSP和越來越多的現場可編程門陣列,即FPGA.

為(wei) 什麽(me) 使用FPGA?

有幾個(ge) 原因推動了FPGA的日益普及。這些原因中的兩(liang) 個(ge) 反映了安防攝像機的最新趨勢,大大增加了需要處理的圖像數據量,第三個(ge) 是經濟方麵原因,即攝像機元器件材料成本(BOM)。

安防攝像機的趨勢:有兩(liang) 個(ge) 主要趨勢正在改變安防攝像機的結構設計方法:

1. 百萬(wan) 像素傳(chuan) 感器的問世

2. 對高(或寬)動態範圍(HDR/WDR)的需要

百萬(wan) 像素傳(chuan) 感器

曾經有一段時間,VGA分辨率傳(chuan) 感器對於(yu) 安防目的的攝像機來說已經足夠了,當時通常由操作人員來監查或者僅(jin) 是存檔以備日後查看。然而,隨著安防攝像頭在全球範圍內(nei) 使用的數量急劇增加,沒有足夠的操作人員來監查,所以安防產(chan) 業(ye) 已經開始依靠軟件來分析視頻,用以監控是否在“關(guan) 注的區域”有任何異常發生,無論是實時的或留作日後分析。複雜的視頻分析(VA)算法已發展到可以將異常情況從(cong) 正常情況中分辨出來;然而,為(wei) 了更加切實有效,這些算法需要比VGA分辨率的攝像機所能提供的更多的細節信息。

攝像機需要更高的分辨率使得VA能夠識別出有限和/或大麵積區域內(nei) 的一般活動,例如:一個(ge) 停車場。一個(ge) 攝像機需要約30像素/輸入用於(yu) 車牌識別,以及約150像素/輸入用於(yu) 查看更細節的活動,如確定收銀機交易。一百萬(wan) 像素涵蓋了7英尺X 7英尺範圍內(nei) 的詳細信息,並且4個(ge) VGA攝像頭才能抵得上一個(ge) 一百萬(wan) 像素的攝像頭。

圖像傳(chuan) 感器已經開發出來並且已經商業(ye) 投產(chan) ,適用於(yu) 1百萬(wan) 、2百萬(wan) 、5百萬(wan) 甚至1千萬(wan) 像素的分辨率。顯然,隨著像素數的增加,因此必須處理的數據量也利用了更高的分辨率這一優(you) 勢。

高動態範圍(HDR)

HDR也稱為(wei) 寬動態範圍(WDR),用以測量傳(chuan) 感器和ISP功能是否能夠很好地區分黑暗和明亮區域。我們(men) 都對業(ye) 餘(yu) 拍攝的以太陽為(wei) 背景的家庭照片非常熟悉。雖然沐浴在陽光下的風景明亮清晰,但是人們(men) 的臉上都非常暗。這是因為(wei) (通常是自動)相機調整在陽光下的場景的曝光。然而,這個(ge) 曝光時間太短,以至於(yu) 無法正確識別較暗的對象。如果手動設定曝光或者使得光圈獲得更多的光線,這樣就能分辨出暗部的細節,但是這樣做的結果是,現在明亮區域的細節已經過度曝光,甚至徹底洗白。這對於(yu) 操作人員或者VA軟件來說都不是一個(ge) 好的結果,因為(wei) 很多關(guan) 注區域的細節信息都已經丟(diu) 失。

HDR傳(chuan) 感器使用創造性的方式解決(jue) 了這個(ge) 問題,根據不同的曝光時間拍攝多張照片,然後通過ISP流水線組合並融合這些圖像,保存並呈現所關(guan) 注區域的亮部和暗部區域的細節信息。顯然,當對於(yu) 同一個(ge) 圖像進行多次曝光,造成了所需處理的數據量增加。例如,當一台攝像機可以輸出每秒60幀的全高清1080p圖像,帶有HDR傳(chuan) 感器,每幀3次曝光,在其工作時,攝像機內(nei) 的ISP流水線實際處理的是60× 3,即相當於(yu) 180幀每秒。

FPGA和增加的處理負荷

一個(ge) 百萬(wan) 像素的傳(chuan) 感器和HDR相結合大大提高了ISP流水線的處理負荷。DSP器件本質上是“順序處理引擎”,很難負荷巨大的數據處理負載。它可能仍然可以處理我們(men) 上述示例中高端DSP中的1080p 60HDR流水線的數據,但成本和功耗高得令人望而卻步,並且在經濟上無法負擔。FPGA由於(yu) 其固有的並行性,非常適合承擔高清、高動態範圍圖像信號處理所增加的負載。

可編程的重要性

除了以極低的功耗和成本提供高性能之外,FPGA定義(yi) 為(wei) 可編程的,這提供了超越ASIC和ASSP的顯著優(you) 點。ASIC的設計和構造都極其昂貴,一旦完成就不能更改。基於(yu) ASSP的攝像頭設計可能會(hui) 受到已經製成的標準件功能的限製,這也就無法再進行修改。事實上,在視頻圖像處理市場中的一些DSP和其它的ASSP器件,需要一個(ge) FPGA來橋接傳(chuan) 感器和標準部件,以適應新的傳(chuan) 感器製造商正在使用的新的串行接口,用於(yu) 接收其傳(chuan) 感器傳(chuan) 輸的百萬(wan) 像素數據。隨著基於(yu) FPGA的實現方法的出現,攝像機製造商可以利用可編程的優(you) 勢,迅速在其設計中采用新的傳(chuan) 感器和技術,或迅速改變他們(men) 的ISP算法。

在FPGA中實現帶有HDR的ISP

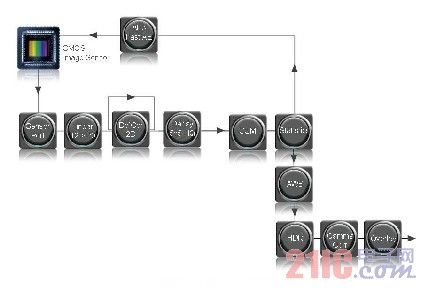

為(wei) 了在FPGA實現帶有HDR的ISP,至少必須實現如圖1所示的圖像信號處理流水線中的ISP塊。

圖1 圖像信號處理流水線

需要以下ISP模塊:

傳(chuan) 感器端口,具有自動的黑電平校正:這對於(yu) 檢測和配置圖像傳(chuan) 感器寄存器和采集圖像數據來說是必需的。

黑電平校正:每個(ge) 顏色通道都有一個(ge) 時間相關(guan) 的偏移。彩色處理需要線性信號處理,因此所有信號必須沒有任何偏移。CMOS圖像傳(chuan) 感器有所謂暗行輸出來衡量每個(ge) 顏色通道的平均偏移。黑電平校正減去專(zhuan) 用彩色通道,基於(yu) 線路的基準噪聲,達到最佳的黑電平結果。

自動曝光:自動曝光模塊的目的是要不斷調整曝光,以適應實時的不斷變化的光線條件。

線性:例如,AptinaMT9Mo24/34 HDR傳(chuan) 感器,每顏色通道輸出20位信息。為(wei) 了盡量減少傳(chuan) 感器輸出的實際線路的數量,Aptina使用智能壓縮機製將這一數據壓縮到12位。線性化就是將這12位數據解壓縮恢複到原來的20位的過程。

缺陷像素校正:由於(yu) 製造工藝而造成的傳(chuan) 感器中死的或熱像素,需要使用缺陷像素校正模塊進行修正。此模塊使用基於(yu) 相同顏色通道的相鄰像素插值法糾正了缺陷的像素值。典型的糾正方法包括冷或熱像素檢測,使用當前像素鄰域中值或平均值估計。

2-D降噪:除冷、熱噪點外,傳(chuan) 感器像素可以隨機成為(wei) 幀噪聲。這意味著它們(men) 輸出與(yu) 鄰近像素相比過高或過低的強度。基於(yu) 相同顏色通道的相鄰像素的插值法進行2D降噪來糾正噪聲像素,與(yu) 缺陷像素校正模塊的工作原理大致類似。

De-Bayering(彩色濾波陣列插值):傳(chuan) 感器上的每個(ge) 像素都有一個(ge) 所謂的Bayer濾波器,使用三種顏色:紅色、綠色或藍色中的一種。因此,三分之二的色彩數據丟(diu) 失,由此產(chan) 生的圖像是三種顏色產(chan) 生的馬賽克。要獲得一個(ge) 全彩色圖像,各種去馬賽克算法,用於(yu) 為(wei) 每個(ge) 像素使用插值算法得到一組完整的紅色、綠色和藍色的值。

色彩校正矩陣(CCM):圖像傳(chuan) 感器通常提供錯誤的顏色再現,由於(yu) 所謂的跨色彩影響,這是由於(yu) 像素間的信號串擾引起的。這種效應會(hui) 導致錯誤顏色的圖像(如:偏藍的綠色)。色彩校正牽涉到複雜的像素數據的矩陣乘法來達到純正的顏色。

自動白平衡(AWB):傳(chuan) 感器不擅長的“識別”色彩。AWB調整圖像中的其他顏色,通過所謂的“灰色世界”算法推斷出圖像中的白色從(cong) 而進行參考。AWB??通過檢查入射光頻率(或波長)來確定白色,並呈現自然色彩的圖像。

伽瑪校正:傳(chuan) 感器像素以線性的方式對入射光強度作出反應。為(wei) 了能夠為(wei) 常見視頻係統提供像素數據,如顯像管的對數響應,可能需要轉化為(wei) 一個(ge) 非線性的值編碼。伽瑪校正提供了這種轉換。#p#分頁標題#e#

高/寬動態範圍(HDR/WDR)處理:這就是將20個(ge) 像素的傳(chuan) 感器數據映射為(wei) 8位RGB數據的模塊,從(cong) 而在顯示出來的圖像中呈現圖像中的明亮和黑暗區域。需要一條寬的內(nei) 部流水線來確保暗部的細節沒有丟(diu) 失,甚至當侵入者直接將閃光照射到攝像機鏡頭。HDR與(yu) 快速自動曝光算法密切配合工作,能在變化的光線條件下迅速調整曝光。

圖2 HDR處理後的圖像:強閃光從(cong) 10英寸的距離直接射到鏡頭,沒有造成圖像丟(diu) 失

下麵表1顯示了在33K查找表(KLUT)、低成本、低功耗的FPGA中實現所有上述ISP模塊所需的FPGA資源的典型值:

除了已經提到的ISP模塊,實際應用的數據包括統計引擎、生成係統中特定模塊使用的圖像柱狀圖、一個(ge) Lattice Mico32軟處理器用於(yu) 動態流水線控製、一個(ge) I2C主控用於(yu) 控製各種信號、一個(ge) HDMI PHY模塊用於(yu) 直接從(cong) FPGA驅動HDMI信號,甚至標誌圖形的疊加。這說明了可以使用低成本、低功耗的FPGA,如Lattice ECP3-35,來實現整個(ge) 圖像信號處理流水線加上HDMI輸出。內(nei) 部HDR流水線為(wei) 32位寬,可以提供192dB (20 log 2**32)的高動態範圍。在這個(ge) 實際的應用中,使用具有120dB動態範圍的傳(chuan) 感器,限製HDR為(wei) 120dB--仍然是任何FPGA可實現的最高值。實際的應用能夠處理每秒60幀的1080p圖像,同時提供120dB的高動態範圍。

在HDR圖像信號處理中使用FPGA的優(you) 點

低成本

如上所述,一個(ge) 簡單的低成本33KLUT FPGA可輕鬆處理一個(ge) 1080p60流水線。使用Lattice ECP3-35實現的1080p60 HDR攝像機的元器件材料主要包括傳(chuan) 感器、FPGA和相關(guan) 的時鍾振蕩器、電阻和電容、穩壓器、一個(ge) HDMI連接器和鏡頭組裝。

高性能

顯示的實現提供了120dB的HDR、1080p60性能、業(ye) 界最快的自動曝光和極高質量的自動白平衡。

低功耗

LatticeECP3與(yu) 競爭(zheng) 對手FPGA或DSP相比,具有極低的靜態和動態功耗。

DDR3支持:FPGA支持DDR3的使用。製造商希望在他們(men) 的設計中加入幀緩衝(chong) 存儲(chu) 器,可以利用這種功能在其攝像機設計中使用高性能、低成本的DDR3存儲(chu) 器。

低功耗的SERDES:一個(ge) 低功耗具有SERDES功能的FPGA使製造商能夠在FPGA中直接實現HDMI PHY,提供HDMI功能,無需增加一塊外部HDMI芯片的成本。

綜述

低成本、低功耗FPGA非常適合用於(yu) 處理安防應用中需要使用百萬(wan) 像素傳(chuan) 感器和攝像機中的HDR功能而引起的信號處理負荷的大量增加。可編程FPGA還提供了前所未有的靈活性。FPGA的實現提供了高動態範圍的高性能ISP流水線,其成本等於(yu) 或低於(yu) 傳(chuan) 統的圖像信號處理方法。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們