0 引言

數字圖象處理技術在電子通信與(yu) 信息處理領域得到了廣泛的應用,設計一種功能靈活、使用方便、便於(yu) 嵌入到係統中的視頻信號采集電路具有重要的實用意義(yi) 。

在研究基於(yu) DSP的視頻監控係統時,考慮到高速實時處理及實用化兩(liang) 方麵的具體(ti) 要求,需要開發一種具有高速、高集成度等特點的視頻圖象信號采集係統,為(wei) 此係統采用專(zhuan) 用視頻解碼芯片和複雜可編程邏輯器件(CPLD)構成前端圖象采集部分。設計上采用專(zhuan) 用視頻解碼芯片,以CPLD器件作為(wei) 控製單元和外圍接口,以FIFO為(wei) 緩存結構,能夠有效地實現視頻信號的采集與(yu) 讀取的高速並行,具有整體(ti) 電路簡單、可靠性高、集成度高、接口方便等優(you) 點,無需更改硬件電路,就可以應用於(yu) 各種視頻信號處理係統中。使得原來非常複雜的電路設計得到了極大的簡化,並且使原來純硬件的設計,變成軟件和硬件的混合設計,使整個(ge) 係統的設計增加柔韌性。

1 係統硬件平台結構

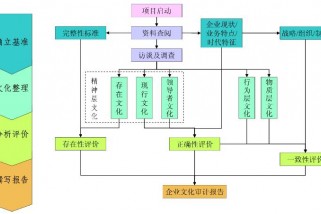

係統平台硬件結構如圖1所示。整個(ge) 係統分為(wei) 兩(liang) 部分,分別是圖象采集係統和基於(yu) DSP主係統。前者是一個(ge) 基於(yu) SAA7110A/SAA7110視頻解碼芯片,由複雜可編程邏輯芯片CPLD實現精確采樣的高速視頻采集係統;後者是通用數字信號處理係統,它主要包括:64K WORD程序存儲(chu) 器、64K WORD數據存儲(chu) 器、DSP、時鍾產(chan) 生電路、串行接口及相應的電平轉換電路等。

係統的工作流程是,首先由圖象采集係統按QCIF格式精確采集指定區域的視頻圖象數據,暫存於(yu) 幀存儲(chu) 器FIFO中;由DSP將暫存於(yu) FIFO中的數據讀入DSP的數據存儲(chu) 器中,與(yu) 原先的幾幀圖象數據一起進行基於(yu) H.263的視頻數據壓縮;然後由DSP將壓縮後的視頻數據平滑地從(cong) 串行接口輸出,由普通MODEM或ADSL MODEM傳(chuan) 送到遠端的監控中心,監控中心的PC機收到數據後進行相應的解碼,並將還原後的視頻圖象進行顯示或進行基於(yu) WEB的廣播。

2 視頻信號采集係統

2.1 視頻信號采集係統的基本特性

一般的視頻信號采集係統一般由視頻信號經箝位放大、同步信號分離、亮度/色度信號分離和A/D變換等部分組成,采樣數據按照一定的時序和總線要求,輸出到數據總線上,從(cong) 而完成視頻信號的解碼,圖中的存儲(chu) 器作為(wei) 幀采樣緩衝(chong) 存儲(chu) 器,可以適應不同總線、輸出格式和時序要求的總線接口。

視頻信號采集係統是高速數據采集係統的一個(ge) 特例。過去的視頻信號采集係統采用小規模數字和模擬器件,來實現高速運算放大、同步信號分離、亮度/色度信號分離、高速A/D變換、鎖相環、時序邏輯控製等電路的功能。但由於(yu) 係統的采樣頻率和工作時鍾高達數十兆赫茲(zi) ,且器件集成度低,布線複雜,級間和器件間耦合幹擾大,因此開發和調試都十分困難;另一方麵,為(wei) 達到精確采樣的目的,采樣時鍾需要和輸人的視頻信號構成同步關(guan) 係,因而,利用分離出來的同步信號和係統采樣時鍾進行鎖相,產(chan) 生精確同步的采樣時鍾,成為(wei) 設計和調試過程中的另一個(ge) 難點。同時,通過實現亮度、色度、對比度、視頻前級放大增益的可編程控製,達到視頻信號采集的智能化,又是以往係統難以完成的。關(guan) 於(yu) 這一點,在係統初期開發過程中已有深切體(ti) 會(hui) [1]。

基於(yu) 以上考慮,本係統采用了SAA7110A作為(wei) 視頻監控係統的輸入前端視頻采樣處理器。

2.2 視頻圖象采集係統設計

SAA7110/SAA7110A是高集成度、功能完善的大規模視頻解碼集成電路[2]。它采用PLCC68封裝,內(nei) 部集成了視頻信號采樣所需的2個(ge) 8bit模/數轉換器,時鍾產(chan) 生電路和亮度、對比度、飽和度控製等外圍電路,用它來替代原來的分立電路,極大地減小係統設計的工作量,並通過內(nei) 置的大量功能電路和控製寄存器來實現功能的靈活配置。SAA7110/SAA7110A可應用的範圍包括桌麵視頻、多媒體(ti) 、數字電視機、圖象處理、可視電話、視頻圖象采集係統等領域。

SAA7110/SAA7110A的控製總線接口為(wei) I2C總線。SAA7110/SAA7110A作為(wei) I2C總線的從(cong) 器件,根據SA管腳的電平,器件的讀寫(xie) 地址可以分別設置為(wei) 9CH/9DH(W/R,SA=0)或9DH/9FH(W/R,SA=1)。其內(nei) 部共計47個(ge) 寄存器,分別控製解碼器(00H~19H)和視頻接口(20H~34H)。通過I2C總線讀、寫(xie) 片內(nei) 的上述寄存器,可以完成輸入通道選擇、電平箝位和增益控製、亮度、色度和飽和度控製等功能。

但是,有一個(ge) 問題必須解決(jue) ,那就是DSP芯片沒有內(nei) 置I2C總線接口,為(wei) 此,本係統提出並采用了對DSP芯片的兩(liang) 個(ge) 可編程I/O引腳進行軟件仿真來實現I2C總線控製的方法。由於(yu) 受C2000程序存儲(chu) 空間最大僅(jin) 有64KB的限製,為(wei) 了減小I2C總線控製仿真軟件的規模,仿真軟件全部用匯編語言完成,因而給本係統的設計帶來了相當的難度和工作量

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們