現在我們(men) 討論幾種可以解決(jue) 由係統噪聲和EMI引起的許多常見問題的技術。

保持電流回路最短

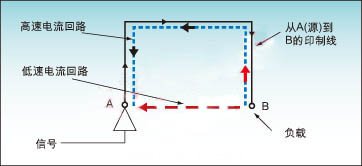

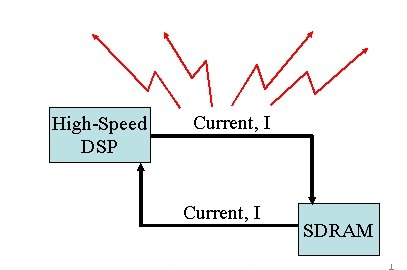

低速信號電流沿阻抗最小,即最短的路徑返回源端。而高速信號則是沿電感最小的路徑返回:這樣的最小的回路麵積位於(yu) 信號線的下麵,如圖1所示。

圖1:高速信號與(yu) 低速信號電流的比較。

因此,高速信號設計的目標之一就是為(wei) 信號電流提供最小的電感回路。這可以利用電源平麵和地平麵來實現。電源平麵通過形成自然的高頻退耦電容將寄生電感降到最小。而地平麵形成一個(ge) 屏蔽麵,即眾(zhong) 所周知的鏡像平麵,能夠提供最短的電流回路。

一種有效的PCB布線方法就是將電源平麵和地平麵靠在一起。這樣形成了高平板電容和低阻抗,有利於(yu) 降低噪聲和輻射。為(wei) 了屏蔽,最好的選擇是:關(guan) 鍵信號最好布到靠近地平麵一邊,而其餘(yu) 的則應靠近電源平麵一側(ce) 。

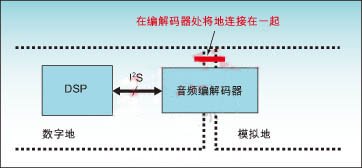

在高速視頻係統中,保持回路短的目的意味著視頻地不能被隔離。而必須被隔離的音頻地,絕不能在數據輸入點處短接到數字地上,如圖2所示。

圖2:音頻地隔離。

電源隔離和鎖相環

如何實現最佳供電是控製噪聲和輻射的最大挑戰。動態負載開關(guan) 環境很複雜,包括的因素有:進入和退出低功率模式;由總線競用和電容器充電所引起的很大的瞬態電流;由於(yu) 退耦和布線不合理引起較大的電壓下降;振蕩器使線性調節器輸出過載。

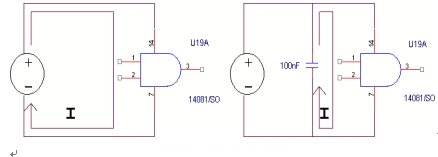

圖3給出了一個(ge) 設計電流回路的實例,其中利用了電源線退耦。該例中的退耦電容盡可能靠近DSP。如果沒有退耦,動態電流回路將較大,這將加大電源電壓的降幅,從(cong) 而產(chan) 生電磁輻射。

圖3:電源退耦。

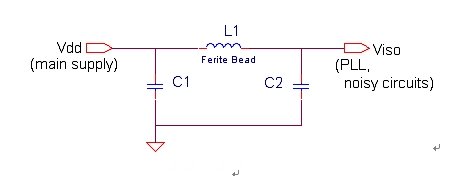

為(wei) PLL供電時,電源隔離是非常重要的,因為(wei) PLL對噪聲非常敏感,並且對於(yu) 穩定係統來說,要求抖動非常低。你還需要選擇模擬的還是數字的PLL,模擬PLL對噪聲的敏感度比數字PLL要低。

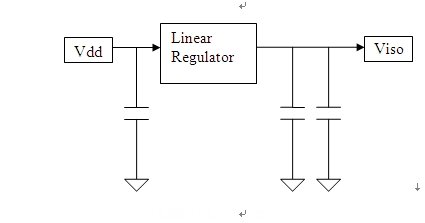

圖4:PLL電源隔離。

如圖4所示的具有低截至頻率的∏型濾波器經常被用來將PLL與(yu) 係統中的其他高速電路隔離開。一個(ge) 較好的辦法是利用一個(ge) 低壓差(LDO)電壓調整器來獨立產(chan) 生PLL的電源電壓,如圖5所示。該方法雖增加了成本,但確保了低噪聲和優(you) 異的PLL性能。

圖5:利用LDO實現PLL電源的隔離。

串擾及傳(chuan) 輸線效應

信號間的幹擾,即串擾,可以通過電磁輻射在印製線間傳(chuan) 播。這也可能由電源和地平麵上的無用信號以電氣的形式產(chan) 生。串擾與(yu) 印製線間距的平方成反比。因此,為(wei) 了將串擾減到最小,單端信號的布線間距應至少是印製線寬度的2倍。對於(yu) 像以太網和USB這類的差分信號,印製線間距需要與(yu) 印製線寬度相同,目的是能夠與(yu) 差分阻抗相匹配。關(guan) 鍵信號可以用地和電源平麵進行屏蔽,或者在改板時增加與(yu) 信號並行的地線。

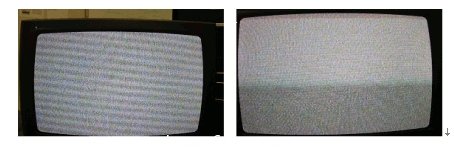

有些信號還產(chan) 生引起串擾的高頻諧波。由於(yu) 輻射的能量正比於(yu) 信號的上升和下降時間,較慢的上升或下降時間引起的幹擾將較小。圖6顯示出視頻幹擾的實例,這些幹擾可能由內(nei) 部時鍾的輻射所引起。在北美地區第二頻道中,18.432MHz的音頻時鍾的三次諧波,將產(chan) 生如圖中左側(ce) 所示的幹擾。通過在音頻時鍾印製線上增加一個(ge) 串聯電阻來放慢時鍾的上升和下降時間,減小了幹擾,其結果如圖6中的右側(ce) 所示。不過,設計師需要了解定時裕度,以便於(yu) 將上升和下降沿降低到係統所允許的限度內(nei) 。

圖6:解決(jue) 音視頻串擾。

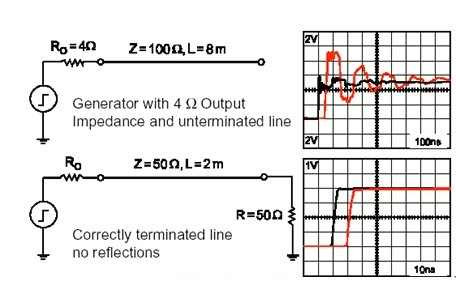

與(yu) 串擾相關(guan) 的是傳(chuan) 輸線效應,這種效應在高速印製線變成產(chan) 生輻射幹擾的發射器時產(chan) 生。通常,當信號的上升時間小於(yu) 傳(chuan) 播延遲的2倍時,印製線才發射信號。這就暗示出了一個(ge) 經驗,即為(wei) 了減小傳(chuan) 播延遲,印製線的長度應盡可能短。另一個(ge) 是合理的信號端接將減慢信號的上升時間,從(cong) 而將反射引起的過衝(chong) 和欠衝(chong) 減到最小。圖7顯示了如何利用並行端接來校正電平並將傳(chuan) 輸線效應減到最小。

圖7:利用端接將傳(chuan) 輸線效應減到最小。

設計師可能會(hui) 質疑,既然芯片內(nei) 部已經集成了電阻,在外部端接負載電阻是否還有其重要性。實際上,除了控製傳(chuan) 輸線效應外,外部電阻還可以實現信號完整性的精密調整。DSP無法與(yu) 電路板阻抗完全匹配,因此端接負載可以減小源電流,以及上升和下降時間。

與(yu) 外部端接負載電阻一樣,外部的上拉和下拉電阻也是重要的。對於(yu) 無連接的引腳來說,雖然內(nei) 部的上拉和下拉電阻是足夠的,但高速開關(guan) 噪聲能夠傳(chuan) 過來,並會(hui) 誤觸發連接端上的內(nei) 部邏輯。

控製EMI

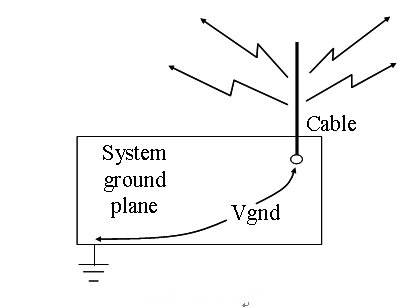

能夠輻射到係統外的輻射被認為(wei) 是EMI,這可能使設計無法通過FCC認證。有兩(liang) 種可能的輻射:一種是發射源是一條直線型的信號印製線,或者電纜的共模輻射,另一種是其信號和回路構成一個(ge) 大電流環路的差分模式輻射。共模輻射隨著頻率的升高而降低,而差分模式輻射則隨著頻率的升高而增強,直到其飽和點。這兩(liang) 種模式的輻射如圖8和9所示。

圖8:共模輻射。

圖9:差模輻射。

如何處理EMI取決(jue) 於(yu) 輻射源。對於(yu) 共模輻射,當EMI來自外部電纜時(例如圖8所示的情況),可以在電纜上加一個(ge) 扼流圈。如果導致EMI的是內(nei) 部傳(chuan) 輸線,則通常用端接負載的方式,不過在信號印製線間加入一條地線也有助於(yu) 減小輻射。另一種可能的方案是將信號的印製線長度減短至小於(yu) 信號波長(或信號頻率的倒數)的1/20。例如,為(wei) 了避免傳(chuan) 輸輻射,500MHz的印製線應該短於(yu) 1.18英寸。

對於(yu) 差分模式輻射,所輻射的能量是電流、環路麵積和頻率的函數。減小輻射的方法包括:端接負載來降低源電流,用合適的電流通道來提供可以減小回路麵積的回路,或者降低頻率。#p#分頁標題#e#

在計算退耦電阻時,還應考慮動態電流。高速電流可能隨時變化,這種瞬變也會(hui) 引起輻射。此外,改變電容器的值時要防止自諧振限製頻率範圍。PCB分層是一個(ge) 好方案,因為(wei) 電源層對高頻形成自然的退耦,而地層則提供最短的回路。把高速信號隔離起來,並使其遠離其他信號。如果可能的話,不要把地層隔開。盡管噪聲和輻射是由係統設計中的複雜的無用功能引起的,但通過上述的一些簡單方法還是可以控製的。

本文小結

高速的DSP視頻係統中有許多潛在的噪聲和輻射源,它們(men) 可以擾亂(luan) 係統的工作,或者使設計通不過FCC的認證。所幸的是,對噪聲和輻射的規劃和掌握可以幫助係統設計師將這些問題減到最小。早期的努力將節省大量的調試工作和後期的麻煩。PCB布局和回路退耦是設計師可以限製係統噪聲和EMI的兩(liang) 種常用技術。具備了這些技術,DSP視頻設計師就能有效地解決(jue) 係統的噪聲和輻射。

作者:Thanh Tran

高級技術專(zhuan) 家

TI公司

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們