在PCB設計中,尤其是在高頻電路中,經常會(hui) 遇到由於(yu) 地線幹擾而引起的一些不規律、不正常的現象。本文對地線產(chan) 生幹擾的原因進行分析,詳細介紹了地線產(chan) 生幹擾的三種類型,並根據實際應用中的經驗提出了解決(jue) 措施。這些抗幹擾方法在實際應用中取得了良好的效果,使一些係統在現場成功運行。

在單片機係統中,PCB(印製電路板)是用來支撐電路元件,並提供電路元件和器件之間電氣連接的重要組件,PCB導線多為(wei) 銅線,銅自身的物理特性也導致其在導電過程中必然存在一定的阻抗,導線中的電感成分會(hui) 影響電壓信號的傳(chuan) 輸,電阻成分則會(hui) 影響電流信號的傳(chuan) 輸,在高頻線路中電感的影響尤為(wei) 嚴(yan) 重,因此,在PCB設計中必須注意和消除地線阻抗所帶來的影響。

1 產(chan) 生幹擾的原因

電阻與(yu) 阻抗兩(liang) 個(ge) 不同的概念。電阻指的是在直流狀態下導線對電流呈現的阻抗,而阻抗指的是交流狀態下導線對電流的阻抗,這個(ge) 阻抗主要是由導線的電感引起的。由於(yu) 地線總是存在阻抗,因此用萬(wan) 用表測量地線時,地線的電阻一般是mmΩ級。

以PCB上一段長10 cm、寬1.5 mm,厚度為(wei) 50μm的導線為(wei) 例,通過計算可得到其阻抗的大小。R=ρL/s(Ω),式中L為(wei) 導線長度(m),s為(wei) 導線截麵積(mm2),ρ為(wei) 電阻率ρ=0.02,因此該導線電阻值約為(wei) 0.026 Ω。

當一段導線與(yu) 其他導線遠離並且其長度遠大於(yu) 寬度時,導線的自感量為(wei) 0.8 μH/m,那麽(me) 10 cm長的導線的電感量是0.08μH。再由下麵的公式求出導線感抗:XL=2πfL,下式中,f為(wei) 導線通過信號的頻率(Hz),L為(wei) 單位長度導線的自感量(H)。所以分別計算出該導線在低頻和高頻下的感抗值:

![]()

在實際電路中,造成電磁幹擾的信號往往是脈衝(chong) 信號,脈衝(chong) 信號包含豐(feng) 富的高頻成分,因此會(hui) 在地線上產(chan) 生較大的電壓。通過以上的公式計算可以看出,在低頻信號傳(chuan) 輸中導線電阻大於(yu) 導線感抗,對於(yu) 數字電路,電路的工作頻率很高,在高頻信號中導線感抗要遠大於(yu) 導線電阻。因此,地線阻抗對數字電路的影響是十分可觀的。這就是電流流過小電阻時產(chan) 生大壓降,導致電路工作異常的原因。

2 地線幹擾機理

2.1 地環路幹擾

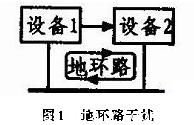

地環路幹擾是一種較常見的幹擾現象,常常發生在通過較長電纜連接並且相距較遠的設備之間。地線造成電磁幹擾的主要原因是地線存在阻抗,當電流流過地線時,會(hui) 在地線上產(chan) 生電壓,這就是地線噪聲。在這個(ge) 電壓的驅動下,會(hui) 產(chan) 生地線環路電流,形成地環路幹擾。如圖1所示是兩(liang) 個(ge) 接地的電路。

由於(yu) 兩(liang) 個(ge) 設備的地電位不同,形成地電壓,在這個(ge) 電壓的驅動下,“設備1一互聯電纜一設備2一地”形成的環路之間有電流流動。由於(yu) 電路的不平衡性,每根導線上的電流不同,因此會(hui) 產(chan) 生差模電壓,對電路造成幹擾。

由於(yu) 地環路幹擾是因地環路電流而導致的,因此有時會(hui) 發現,當把一個(ge) 設備的地線斷開後,幹擾現象消失,這是因為(wei) 地線斷開時切斷了地環路。這種現象經常發生在低頻幹擾的場合,當幹擾頻率較高時,斷開地線與(yu) 否關(guan) 係不大。

2.2 公共阻抗幹擾

在數字電路中,由於(yu) 信號的頻率較高,地線往往呈現較大的阻抗。這時,當幾個(ge) 電路共用一段地線時,由於(yu) 地線的阻抗,一個(ge) 電路的地電位會(hui) 受另一個(ge) 電路工作電流的調製,這樣一個(ge) 電路中的信號會(hui) 耦合進另一個(ge) 電路,這種耦合稱為(wei) 公共阻抗耦合。

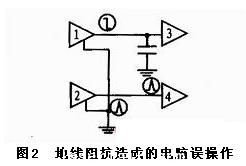

解決(jue) 公共阻抗耦合的方法是減小公共地線部分的阻抗,或采用單點接地,徹底消除公共阻抗圖2的例子說明了一種幹擾現象。圖2是一個(ge) 有四個(ge) 門電路組成的簡單電路。假設門1的輸出電平由高變為(wei) 低,這時電路中的寄生電容(有時門2的輸入端有濾波電容)會(hui) 通過門1向地線放電,由於(yu) 地線的阻抗,放電電流會(hui) 在地線上產(chan) 生尖峰電壓,如果這時門3的輸出是低電平,則這個(ge) 尖峰電壓就會(hui) 傳(chuan) 到門3的輸出端,門4的輸入端,如果這個(ge) 尖峰電壓的幅度超過門4的噪聲門限,就會(hui) 造成門4的誤動作。

2.3 地環路電磁耦合幹擾

圖1所示的“地線環路”將包圍一定的麵積,根據電磁感應定律,如果這個(ge) 環路所包圍的麵積中有變化的磁場存在,就會(hui) 在環路中產(chan) 生感生電流,形成幹擾。空間磁場的變化無處不在,於(yu) 是包圍的麵積越大幹擾就越嚴(yan) 重。

3 解決(jue) 地線幹擾的方法

3.1 解決(jue) 地環路幹擾

解決(jue) 地環路幹擾的基本思路有3個(ge) :一個(ge) 是減小地線的阻抗,從(cong) 而減小幹擾電壓,但是這對第二種原因導致的地環路幹擾沒有效果。第二個(ge) 方法是改變接地結構,將一個(ge) 機箱的地線連接到另一個(ge) 機箱上,通過另一個(ge) 機箱接地,這就是單點接地的概念。第三個(ge) 是增加地環路的阻抗,從(cong) 而減小地環路電流。當阻抗無限大時,實際是將地環路切斷,即消除了地環路。因此提出以下幾種解決(jue) 地環路幹擾的方案。

1)將一側(ce) 的設備浮地

如果將一側(ce) 電路浮地,就切斷了地環路,因此可以消除地環路電流。但有兩(liang) 個(ge) 問題需要注意,一個(ge) 是出於(yu) 安全的考慮,不允許電路浮地。這時可以考慮將設備通過一個(ge) 電感接地。這樣對於(yu) 50 Hz的交流電流設備接地阻抗很小,而對於(yu) 頻率較高的幹擾信號,設備接地阻抗較大,減小了地環路電流。但這樣做隻能減小高頻幹擾的地環路幹擾。另一個(ge) 問題是,盡管設備浮地,但設備與(yu) 地之間還是有寄生電容,這個(ge) 電容在頻率較高時會(hui) 提供較低的阻抗,因此並不能有效地減小高頻地環路電流。

2)使用變壓器

解決(jue) 地環路幹擾的最基本方法是切斷地環路。用隔離變壓器就起到這個(ge) 作用,兩(liang) 個(ge) 設備之間的信號傳(chuan) 輸通過磁場耦合進行,而避免了電氣直接連接。這時地線上的幹擾電壓出現在變壓器的初次級之間,而不是在電路的輸入端。提高變壓器高頻隔離效果的一個(ge) 辦法是在變壓器的初次級之間設置屏蔽層。但一定要注意隔離變壓器屏蔽層的接地端必須在接受電路一端。否則,不僅(jin) 不能改善高頻隔離效果,還可能使高頻耦合更加嚴(yan) 重。因此,變壓器要安裝在信號接收設備的一側(ce) 。

變壓器隔離的方法有一些缺點,不能傳(chuan) 輸直流,體(ti) 積大,成本高。由於(yu) 變壓器的初次級之間有寄生電容,因此高頻時的隔離效果不是很好。#p#分頁標題#e#

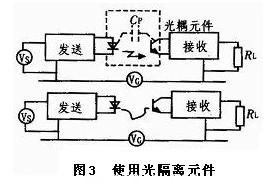

3)使用光隔離元件

用光傳(chuan) 輸信號是解決(jue) 地環路問題的理想方法。如圖3所示,光耦器件的寄生電容為(wei) 2 pF左右,因此能夠在很高的頻率起到隔離作用。如果使用光纖,則沒有寄生電容的問題,能夠獲得十分完善的隔離效果。但是,用光纖會(hui) 帶來其它問題,如:需要更大的功率、需要更多的外圍器件,光連接的線形和動態範圍都達不到模擬信號的要求、光纜的安裝和維護比較複雜等,使用時應注意。

4)使用共模扼流圈

地線電壓實際是一種共模電壓,在這個(ge) 電壓的驅動下,電纜中流過的電流是共模電流。在連接電纜上使用共模扼流圈相當於(yu) 增加了地環路的阻抗,這樣在一定的地線電壓作用下,地環路電流會(hui) 減小。但要注意控製共模扼流圈的寄生電容,否則對高頻幹擾的隔離效果很差。共模扼流圈的匝數越多,則寄生電容越大,高頻隔離的效果越差。

5)平衡電路對地環路幹擾的抑製

平衡電路的定義(yi) 是兩(liang) 個(ge) 導體(ti) 及其所連接的電路相對於(yu) 地線或其他參考物體(ti) 具有相同的阻抗。

高頻時平衡是很困難的,實際的電路會(hui) 有很多寄生因素,如寄生電容、電感等。這些參數在頻率較高時對電路阻抗發揮著較大作用。由於(yu) 這些寄生參數的不確定性,電路的阻抗也是不確定的,因此很難保證兩(liang) 個(ge) 導體(ti) 的阻抗完全相同。因此,在高頻時,電路平衡性往往較差,這意味著:平衡電路對頻率較高的地環路電流幹擾抑製效果較差。

3.2 消除公共阻抗耦合

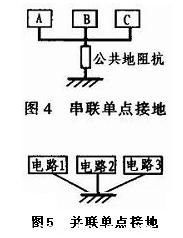

消除公共阻抗耦合的途徑有兩(liang) 個(ge) ,一個(ge) 是減小公共地線部分的阻抗,這樣公共地線上的電壓也隨之減小,從(cong) 而控製公共阻抗耦合。另一個(ge) 方法是通過適當的接地方式避免容易相互幹擾的電路共用地線,一般要避免強電電路與(yu) 弱電電路共用地線,數字電路與(yu) 模擬電路共用地線等。並聯接地的缺點是接地的導線過多。因此在實際中,沒有必要所有電路都並聯單點接地,對於(yu) 相互幹擾較少的電路,可以采用串聯單點接地。例如,可以將電路按照強信號,弱信號,模擬信號,數字信號等分類,然後在同類電路內(nei) 部用串聯單點接地,如圖4所示,不同類型的電路采用並聯單點接地,如圖5所示。當信號頻率低於(yu) 1 MHz時可采用單點接地的方法,使其不形成回路。信號頻率高於(yu) 10 MHz時最好采用多點接地,盡量降低地線阻抗。電源線與(yu) 地線應盡量靠近走線以減少所包圍的環路麵積,從(cong) 而減少外界磁場對環路切割產(chan) 生的電場幹擾,同時也減少環路對外電磁輻射。

如前所述,減小地線阻抗的核心問題是減小地線的電感。可以使用扁平導體(ti) 做地線,或用多條相距較遠的並聯導體(ti) 作接地線。對於(yu) PCB,在雙層板上布地線網格能夠有效地減小地線阻抗,在多層板中可以專(zhuan) 門用一層做地線來減小阻抗。

4 結論

抗幹擾設計是單片機係統設計的重要環節,其設計的好壞往往決(jue) 定整個(ge) 係統的成敗。關(guan) 於(yu) 接地,許多關(guan) 於(yu) 電磁兼容的專(zhuan) 著中都有詳細的論述,但是,最好的接地方式應該是通過試驗來選定的,地線幹擾也要通過試驗來查找和排除。本文介紹了地線引起幹擾的原因和解決(jue) 方法,說明了地線設計中的一般方法和原則,隻有在理論的指導下,經過大量的試驗過程和經驗積累才能更好地掌握接地係統的設計方法和幹擾排除手段,從(cong) 而更好的提高電路工作的可靠性。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們