摘要:

隨著現代電子技術的發展以及芯片的高速化和集成化,各種電子設備係統內(nei) 外的電磁環境更加複雜,因此在印製電路板的電路設計階段考慮電磁兼容性( EMC) 設計是非常重要的。 以12層板為(wei) 例討論了多層PCB分層方法、布線的規則、地線和電源線布置以及電磁兼容性。

電磁兼容(Electro - Magnetic Compatibility,簡稱EMC)是一門新興(xing) 綜合性學科,它主要研究電磁幹擾和抗幹擾問題。 電磁兼容性是指電子設備或係統在規定的電磁環境電平下,不因電磁幹擾而降低性能指標,同時它們(men) 本身產(chan) 生的電磁輻射不大於(yu) 限定的極限電平,不影響其它係統的正常運行,並達到設備與(yu) 設備、係統與(yu) 係統之間互不幹擾、共同可靠工作的目的。 電磁幹擾( EM I)產(chan) 生是由於(yu) 電磁幹擾源通過耦合路徑將能量傳(chuan) 遞給敏感係統造成的,它包括由導線和公共地線的傳(chuan) 導、通過空間輻射或近場耦合3種基本形式。 實踐證明,即使電路原理圖設計正確,印製電路板設計不當,也會(hui) 對電子設備的可靠性產(chan) 生不利影響,所以保證印製電路板電磁兼容性是整個(ge) 係統設計的關(guan) 鍵,本文主要討論電磁兼容技術及其在多層印製線路板( Printed Circuit Board,簡稱PCB)設計中的應用。

PCB是電子產(chan) 品中電路元件和器件的支撐件,它提供電路元件和器件之間的電氣連接,是各種電子設備最基本的組成部分。 如今,大規模和超大規模集成電路已在電子設備中得到廣泛應用,而且元器件在印刷電路板上的安裝密度越來越高,信號的傳(chuan) 輸速度更是越來越快, 由此而引發的EMC問題也變得越來越突出。 PCB 有單麵板(單層板) 、雙麵板(雙層板)和多層板之分。 單麵板和雙麵板一般用於(yu) 低、中密度布線的電路和集成度較低的電路, 多層板使用高密度布線和集成度高的電路。 從(cong) 電磁兼容的角度看單麵板和雙麵板不適宜高速電路,單麵、雙麵布線已滿足不了高性能電路的要求,而多層布線電路的發展為(wei) 解決(jue) 以上問題提供了一種可能,並且其應用變得越來越廣泛。

1 多層布線的特點

PCB是由具有多層結構的有機和無機介質材料組成,層之間的連接通過過孔來實現,過孔鍍上或填充金屬材料就可以實現層之間的電信號導通。 多層布線之所以得到廣泛的應用,究其原因,有以下特點:

(1)多層板內(nei) 部設有專(zhuan) 用電源層、地線層。 電源層可以作為(wei) 噪聲回路,降低幹擾;同時電源層還為(wei) 係統所有信號提供回路,消除公共阻抗耦合幹擾。 減小了供電線路的阻抗,從(cong) 而減小了公共阻抗幹擾。

(2)多層板采用了專(zhuan) 門地線層,對所有信號線而言都有專(zhuan) 門接地線。 信號線的特性:阻抗穩定、易匹配,減少了反射引起的波形畸變;同時,采用專(zhuan) 門的地線層加大了信號線和地線之間的分布電容,減小了串擾。

2 印製電路板的疊層設計

2. 1 PCB的布線規則

多層電路板的電磁兼容分析可以基於(yu) 克希霍夫定律和法拉第電磁感應定律。 根據克希霍夫定律, 任何時域信號由源到負載的傳(chuan) 輸都必須有一個(ge) 最低阻抗的路徑。

具有多層的PCB常常用於(yu) 高速、高性能的係統,其中的多層用於(yu) 直流(DC)電源或地參考平麵。 這些平麵通常是沒有任何分割的實體(ti) 平麵,因為(wei) 具有足夠的層用作電源或地層,因此沒有必要將不同的DC電壓置於(yu) 同一層上。 該層將會(hui) 用作與(yu) 它們(men) 相鄰的傳(chuan) 輸線上信號的電流返回通路。 構造低阻抗的電流返回通路是這些平麵層最重要的EMC目標。

信號層分布在實體(ti) 參考平麵層之間,它們(men) 可以是對稱的帶狀線和非對稱的帶狀線。 以一個(ge) 12層板為(wei) 例說明多層板的結構和布局 。 其分層結構為(wei) T - P - S - P - S - P - S - P - S - S - P - B,“T”為(wei) 頂層,“P”為(wei) 參考平麵層,“S”為(wei) 信號層,“B”為(wei) 底層。 從(cong) 頂層至底層依次為(wei) 第1層、第2層、??第12層。 頂層和底層用作元件的焊盤,信號在頂層和底層不應傳(chuan) 輸太長的距離,以便減少來自走線的直接輻射。 不相容的信號線應相互隔離,這樣做的目的是避免相互之間產(chan) 生耦合幹擾。 高頻與(yu) 低頻、大電流與(yu) 小電流、數字與(yu) 模擬信號線是不相容的, 元件布置中就應該把不相容元件放在印製板上不同的位置, 在信號線的布置上仍要注意把它們(men) 隔離。 設計時要注意以下3個(ge) 問題:

(1)確定哪個(ge) 參考平麵層將包含用於(yu) 不同的DC電壓的多個(ge) 電源區。 假設第11層有多個(ge) DC電壓,就意味著設計者必須將高速信號盡可能遠離第10層和底層,因為(wei) 返回電流不能流過第10層以上的參考平麵,並且需要使用縫合電容,第3、5、7和9層分別為(wei) 高速信號的信號層。 重要信號的走線盡可能以一個(ge) 方向布局,以便優(you) 化層上可能的走線通道數。 分布在不同層上的信號走線應互相垂直,這樣可以減少線間的電場和磁場的耦合幹擾,第3和第7層可以設定為(wei) “東(dong) 西”走線,而第5和第9層設置為(wei) “南北”走線。 走線布在哪一層要根據其到達目的地的方向。

(2)高速信號走線時層的變化,及哪些不同的層用於(yu) 一個(ge) 獨立的走線,確保返回電流從(cong) 一個(ge) 參考平麵流到需要的新參考平麵。 這樣是為(wei) 了減小信號環路麵積,減小環路的差模電流輻射和共模電流輻射。 環路輻射與(yu) 電流強度、環路麵積成正比。 實際上,最好的設計並不要求返回電流改變參考平麵,而是簡單地從(cong) 參考平麵的一側(ce) 改變到另一側(ce) 。 如信號層的組合可以用作信號層對:第3層和第5層,第5層和第7層,第7層和第9層,這就允許一個(ge) 東(dong) 西方向和南北方向形成一個(ge) 布線組合。 但是第3層和第9層的組合就不應使用,因為(wei) 這要求返回電流從(cong) 第4層流到第8層。 盡管一個(ge) 去耦電容可以放置在過孔附近,但在高頻時由於(yu) 存在引線和過孔電感而使電容失去作用。 並且這種走線會(hui) 使信號環路麵積增大,不利減小電流輻射。

(3)為(wei) 參考平麵層選定DC電壓。 該例中,由於(yu) 處理器內(nei) 部信號處理的高速性,致使在電源/地參考引腳上存在大量的噪聲。 因此,在為(wei) 處理器提供相同DC電壓上使用去耦電容器非常重要,並且盡可能有效地使用去耦電容器。 降低這些元件電感的最好方法是連接走線盡可能短和寬,並且盡可能使過孔短和粗。

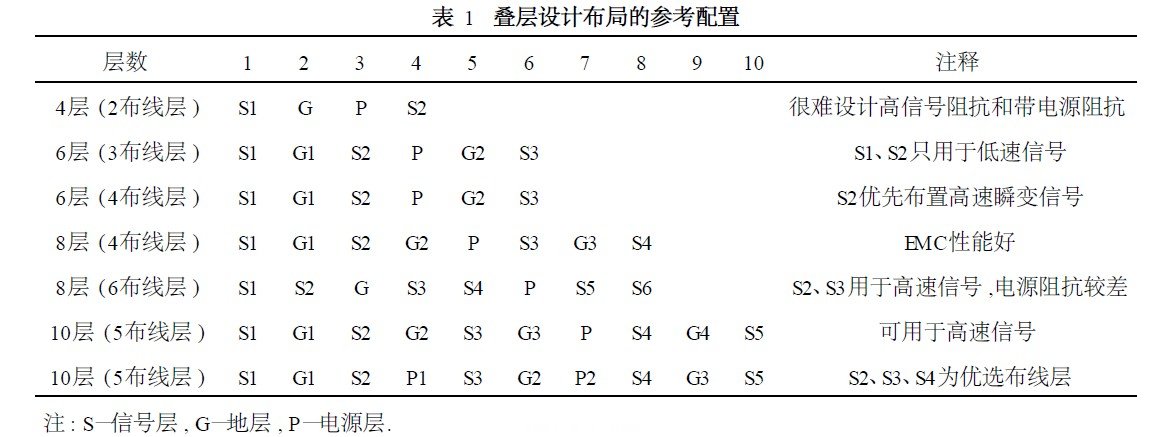

如果第2層分配為(wei) “地”,且第4層分配為(wei) 處理器的電源,則過孔距離放置處理器和去耦電容器的頂層應該盡可能短。 延伸到板的底層的過空剩餘(yu) 部分不包含任何重要的電流,而且距離短不會(hui) 具有天線作用。 表1列出了疊層設計布局的參考配置。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們