2. 2 20 - H規則及3 -W 法則

在多層PCB板電磁兼容性設計中,確定多層板電源層與(yu) 邊沿的距離和解決(jue) 印製條間的距離有兩(liang) 個(ge) 基本原則: 20 - H規則及3 - W法則 。

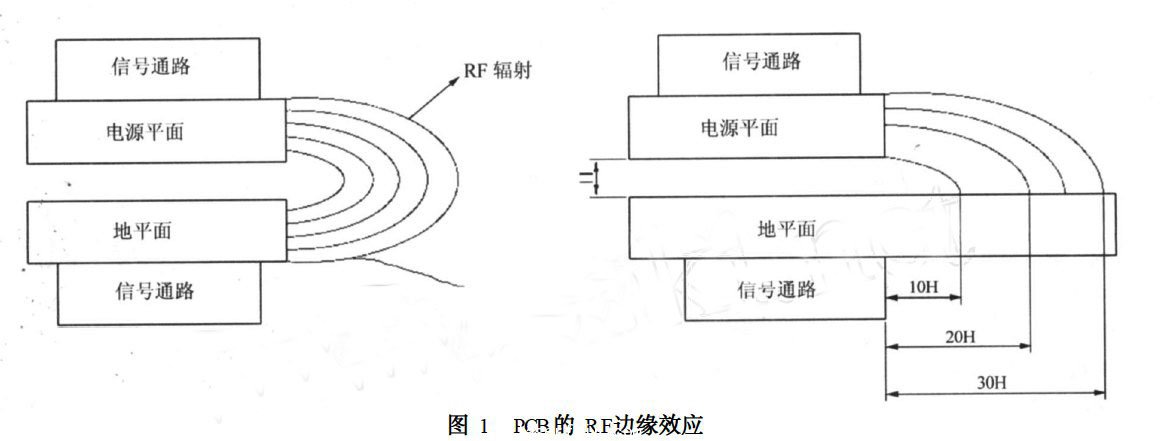

20 - H原則:由於(yu) 磁通之間的連接, RF電流通常存在於(yu) 電源平麵的邊緣,這種層間的耦合稱為(wei) 邊緣效應,當使用高速的數字邏輯和時鍾信號時,電源平麵間會(hui) 互相耦合RF電流,如圖1所示。 為(wei) 減小這種效應,電源平麵的物理尺寸都應該比最靠近地平麵的物理尺寸至少小20H (H為(wei) 電源平麵和地平麵之間的距離) ,電源的邊緣效應通常發生在10H左右, 20H時約10%的磁通被阻斷,如果想達到98%磁通被阻斷的話,則需要100%的邊界值,如圖1所示。 20 - H規則決(jue) 定了電源平麵和最近的接地平麵間的物理距離,這個(ge) 距離包括敷銅厚度、預填充和絕緣分離層。 使用20 - H可以提高PCB自身的諧振頻率。

3 - W法則:當兩(liang) 條印製線間距較小時,兩(liang) 條線之間會(hui) 發生電磁串擾,這會(hui) 使有關(guan) 電路功能失常,為(wei) 避免這種幹擾,應保持任何線條間距不小於(yu) 3倍印製線條寬度,即不小於(yu) 3W (W為(wei) 印製線條寬度)。 印製線條寬度取決(jue) 於(yu) 線條阻抗的要求,太寬會(hui) 影響布線密度,太窄會(hui) 影響傳(chuan) 輸到終端的信號完整性和強度。 時鍾電路、差分對、I/O端口的布線都是3 - W原則的基本應用對象。 3 - W原則隻是表示了串擾能量衰減70%的電磁通量線邊界,若要求更高,如保證串擾能量衰減98%的電磁通量邊界線就必須采用10W間隔。

2. 3 地線的布置

首先,要建立分布參數的概念,高於(yu) 一定頻率時, 任何金屬導線都要看成是由電阻、電感構成的器件 。 所以接地引線具有一定阻抗並且構成電氣回路,不管是單點接地還是多點接地, 都必須構成低阻抗回路進入真正的地或機架。 25mm 長的典型印製線大約會(hui) 表現15~ 20nH電感,加上分布電容的存在,就會(hui) 在接地板和設備機架之間構成諧振電路。 其次, 接地電流流經接地線時,會(hui) 產(chan) 生傳(chuan) 輸線效應和天線效應。 當線條長度為(wei) 1 /4波長時,表現出很高的阻抗,接地線實際上是開路的, 接地線反而成為(wei) 向外輻射的天線。 最後,接地板上充滿高頻電流和騷擾形成的渦流,因此,在接地點之間構成許多回路,這些回路的直徑(或接地點間距) 應小於(yu) 最高頻率波長的1 /20. 選擇恰當的器件是設計成功的重要因素,特別是在選擇邏輯器件時,盡量選擇上升時間比5ns長的, 決(jue) 不要選比電路要求時序快的邏輯器件。

#p#分頁標題#e# 2. 4 電源線的布置

對於(yu) 多層板, 采用電源層- 地層結構供電,這種結構的特性阻抗比軌線對小得多,可以做到小於(yu) 1Ω。 這種結構具有一定的電容,不必在每個(ge) 集成芯片旁加高頻去耦電容。 即使層電容容量不夠,需要外加去耦電容時,也不要加在集成芯片旁邊,可加在印製板的任何地方。 集成芯片的電源腳和地腳可以通過金屬化通孔直接與(yu) 電源層和地層連接, 所以供電環路總是最小的。 由於(yu) “電流總是走阻抗最小途徑”原則, 地層上的高頻回流總是緊貼在軌線下麵走, 除非有地層隔縫阻擋, 因此信號環路也總是最小的。 可見電源層- 地層結構與(yu) 軌線對供電相比較, 具有布置簡單靈活、電磁兼容性好等優(you) 點。

3 結束語

總之,在多層PCB設計中,元器件要分組放置, 以防止產(chan) 生組間幹擾; 高速電路位置要安排恰當, 以免通過電場耦合或磁場耦合幹擾其他電路; 根據情況分別設置地線, 以防止共地線阻抗耦合幹擾; 供電環路麵積應該減小到最低程度, 且不同電源的供電環路不要重疊, 以避免產(chan) 生磁場耦合;不相容的信號線要相互隔離, 以免產(chan) 生耦合幹擾; 還應減小信號環路麵積, 以降低環路輻射和共模輻射.

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們