由於(yu) 目前很多單片機的I/O口具備了15mA以上的驅動能力且價(jia) 格比較便宜,因此在大屏幕的設計中也采用多處理器方案。係統的基本特點是:一個(ge) 顯示組中有多個(ge) 處理器,包括一個(ge) 主CPU和多個(ge) 子CPU,其結構示意圖如圖3 所示。主CPU的任務是通過數據采集或與(yu) 外界通信等獲取顯示信息,再傳(chuan) 輸給子CPU,主CPU還負責行掃描和發送顯示同步信息等。子CPU接收主CPU的數據信息並存放到內(nei) 部RAM.中,再根據主CPU發出的控製信息選擇適當的列輸出口進行列掃描。假設每個(ge) 子CPU可用作輸出口的最多引腳數為(wei) m,而每塊LED矩陣的列數為(wei) n,則每塊芯片所能驅動的LED塊最大數為(wei) m/n 這樣,每個(ge) 單片機負責一塊或幾塊》LED塊,靈活性強,便於(yu) 擴展,同時減輕了主CPU的負擔,提高了點陣的刷新頻率。

圖3 多CPU控製電路結構示意圖

在多畫麵顯示的大屏幕設計中,這種方案較為(wei) 理想,對不同的顯示畫麵采用單獨的子CPU進行列掃描,再通過主CPU進行統一的行掃描,雖然控製電路使用的元件較多,但電路結構簡單,易於(yu) 實現。

2.2 基於(yu) CPLD/FPGA的控製電路設計方案

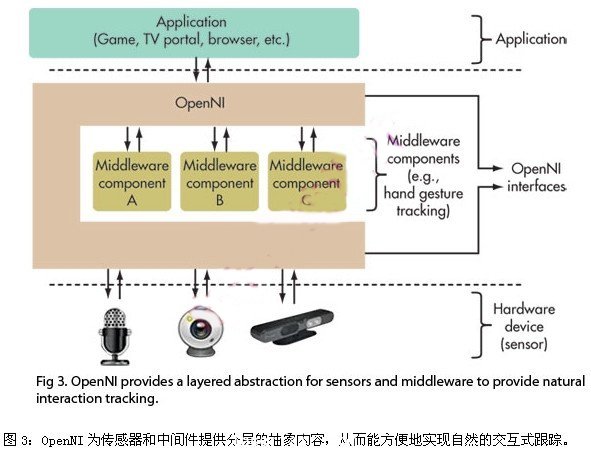

頻圖像信號頻率高:數據量大,要求實時處理,加之LED大屏幕電路的數字邏輯相當複雜,采用CPLD/FPGA設計控製電路,可以簡化係統結構,便於(yu) 調試。 圖3是CPLD/FPGA設計控製電路的原理圖。采用CPLD/FPGA器件對其中的同步控製、主從(cong) 控製、讀寫(xie) 控製和灰度調製等大量電路進行了集成,使圖像數據處理更為(wei) 快速,圖像更加穩定,而且係統結構緊湊,工作可靠性有所提高。

虛線以外的其它功能模塊均有CPLD/FPGA編程實現,將複雜的硬件電路設計通過軟件編程來取代。與(yu) 圖2的單片機控製電路對比來看,電路結構明顯更簡潔,電路的麵積減小及可靠性增強,調試也更為(wei) 簡單,由於(yu) CPLD/FPGA可以並行處理多個(ge) 進程,比起單片機對任務的順序處理效率更高,點陣的刷新頻率也隨之提高。

此外,可編程邏輯器件的片內(nei) 資源越來越豐(feng) 富,許多器件內(nei) 部都集成了RAM塊,以Altera公司推出的高性價(jia) 比FPGA颶風EP1C6為(wei) 例,它的內(nei) 部就集成了20塊RAM.模塊,每塊容量為(wei) 4Kbit,這些RAM塊可通過軟件設置成單端口RAM.,雙端口RAM,FIFO等,滿足係統對數據處理的需要。比如在設計灰度調製器時,色彩再現的灰度等級越高,在保持相同的刷新頻率的情況下,對數據的處理速度越高,此時,可以將FPGA的內(nei) 部RAM.塊設置成一個(ge) 雙端口RAM.作為(wei) 灰度調製的緩衝(chong) 區,在讀取幀存儲(chu) 器中的數據的同時,將上次讀取的數據進行灰度調製,二者交替進行,加快了數據的處理速率。在顯示係統集成度和穩定性要求較高:圖像灰度級較多的大屏幕設計中,采用可編程邏輯器件設計控製電路更方便。

另有一些控製電路的設計方案綜合運用了單片機技術和EDA技術,利用單片機實現數據的處理、存儲(chu) 和通信功能,CPLD/FPGA實現數據的灰度調製、掃描顯示等功能。這種方案對單片機和CPLD/FPGA的資源要求都不是很高,電路設計也相對較容易,既保證了顯示效果,又節約了設計成本。#p#分頁標題#e#

2.3嵌入式係統在大屏幕設計中的應用

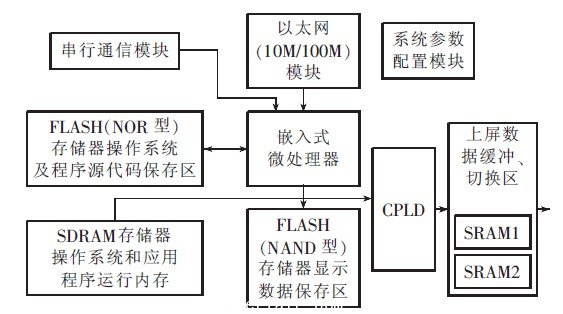

由於(yu) 嵌入式計算機技術具有單片機無法比擬的優(you) 點:指令執行速度比普通單片機高一個(ge) 數量級,支持大容量的存儲(chu) 空間:寬範圍的存儲(chu) 器接口類型,高位寬的數據總線,多種外設通信接口,特別是嵌入式操作係統的使用可以更為(wei) 有效的管理係統資源的分配,通過其高效的調度算法,使得整個(ge) 應用程序的設計可以采用多任務的方式實現,極大地提高了係統的運行速度和可靠性。 基於(yu) Linux的嵌入式係統的控製電路設計如圖5所示。

圖5 基於(yu) Linux的嵌入式係統控製電路原理圖

2.4大屏幕顯示的驅動方案

LED大屏幕的驅動方案主要有三種#串行控製驅動方式:並行控製驅動方式以及應用高度集成專(zhuan) 用芯片驅動。 串行控製驅動方式是將顯示的數據通過串行方式送入點陣驅動電路,其特點是線路連接簡單,調試方便,單元的可靠性也較高,串行控製驅動方式可選用的芯片有:MC4094,74LS595,9094等,行驅動要求功率較大,一般采用大功率三極管來驅動,行掃描可用三-八譯碼器等控製,由於(yu) 串入並出芯片可級聯,為(wei) LED單元的級聯提供了支持。

並行控製驅動方式將顯示的數據通過並行方式送入點驅動電路,其優(you) 點是數據的刷新速率快。 並行驅動方式可選74LS374這類的鎖存芯片,采用首尾相連的方式將控製:驅動一並形成。 並行驅動方案控製方便,係統投入成本低。 高度集成的專(zhuan) 用驅動芯片例如ZQL9701集行:列控製及一些外圍驅動電路於(yu) 一身,使單元的控製:驅動更為(wei) 簡單,係統的穩定性更為(wei) 可靠,采用ZQL9701將使係統的顯示灰度達到256級,但係統成本較高。 對於(yu) 中小規模的生產(chan) 和應用應以前兩(liang) 種驅動方案為(wei) 主,規模化生產(chan) 以及要求較高的應用場合可選用專(zhuan) 用集成芯片驅動。

3 結束語

LED大屏幕控製電路的設計方案各具特色,實際工程應用中可根據需要選擇不同的設計方案,設計單色及灰度等級不高的大屏幕時,可采用基於(yu) 單片機的設計方案,要實現高難度圖文動態特技顯示和多灰度級顯示時,則應選擇基於(yu) 可編程邏輯器件的設計方案或基於(yu) 嵌入式技術的設計方案。#p#分頁標題#e#

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們