1引言

視覺測量技術是以機器視覺技術為(wei) 基礎,融合電子技術、計算機技術、近景攝影測量技術、圖像處理技術為(wei) 一體(ti) 的測量技術,其基本任務是以測量為(wei) 目的,從(cong) 圖像信息出發計算三維空間中物體(ti) 的幾何信息。其中,圖像處理技術是視覺測量係統中最重要的一部分,也是本文的研究重點。

傳(chuan) 統的視覺測量係統主要是在 PC機上采用軟件方式實現,由於(yu) 其專(zhuan) 用性不夠高,因此處理速度較慢。近年來,基於(yu) FPGA的SOPC技術的出現,使 FPGA高效的硬件並行信號處理能力和軟件控製的靈活性完美的結合到一起。在SOPC係統中,對速度要求高的算法可以采用自定義(yi) 硬件邏輯的方法實現;而用硬件難以實現的複雜算法以及控製流程可以在 Nioses II核中以軟件方式實現。因此基於(yu) SOPC技術的係統具有很好的實時性、靈活性以及可擴展性。設計者可以自由的進行軟硬協同設計,並且可以在設計的各個(ge) 階段不受限製的修改設計而無需重新構建硬件平台。

本文所討論的 SOPC係統是大尺寸三維視覺測量係統的一部分,以 PCI板卡的形式內(nei) 嵌在PC機中。在整個(ge) 大尺寸三維視覺測量係統中,采用數字相機從(cong) 不同位置拍攝多幅圖像,經過特征點提取、點中心的二維坐標計算、特征點匹配、三維拚接、麵形擬合等步驟,得到被測物體(ti) 的三維麵形信息。點中心的計算精度直接影響測量精度,且其計算速度一直是係統的瓶頸之一。為(wei) 提高處理速度和計算精度,采用SOPC係統完成特征點提取和點中心計算,其結果通過 PCI總線上傳(chuan) 給 PC機,由其上的軟件模塊完成後續的計算和處理工作。

2 SOPC係統的總體(ti) 設計方案

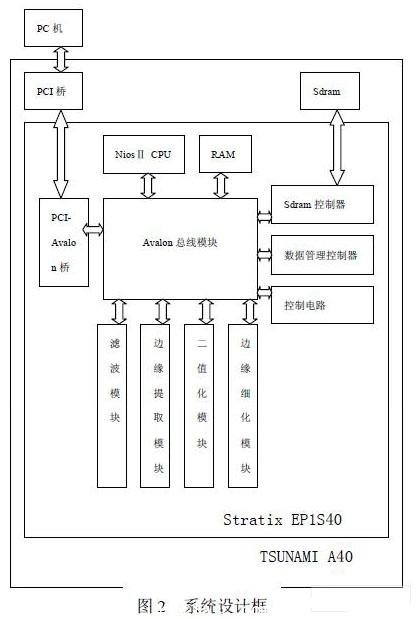

本係統采用加拿大 SBS公司的 TSUNAMI A40係列開發板,其核心的 FPGA模塊是 Altera公司的 Stratix EP1S40芯片。

2.1 係統算法的基本原理

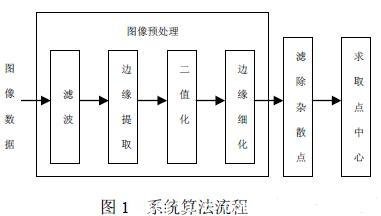

係統算法實現流程如圖1所示。首先,針對本係統圖像處理的要求與(yu) 算法實現特點進行軟硬件劃分。圖像預處理部分所需要處理的數據量比較大,但算法相對簡單,可以通過FPGA自定義(yi) 相應的 IP模塊,采用硬件的方式實現;後續處理部分由於(yu) 算法相對複雜,用硬件實現比較困難,而且其數據處理量不大,所以采用在Nioses II軟核中以軟件的方式實現。最後編寫(xie) 係統控製軟件對整個(ge) 係統進行控製使軟硬件協同工作。

2.2 係統硬件的設計方案

如圖 2所示,本係統硬件開發板通過 PCI橋與(yu) PC機相連,原始圖片保存在 PC機中。 PCI-Avalon橋是 PC機與(yu) FPGA開發板的通信接口,圖像數據經過 PCI-Avalon橋進入係統處理模塊。Sdram管理控製器用來管理和控製Sdram中的數據存取。控製電路用來控製與(yu) 協調各個(ge) 外設的運行,實現狀態控製與(yu) 數據傳(chuan) 輸等基本操作,包括讀取Sdram中保存的圖像數據,控製圖像處理各模塊。 Sdram用來保存圖像數據。原始圖像數據最初由 PC機下載到 Sdram中,再通過Sdram管理控製器傳(chuan) 輸給各處理模塊依次處理。處理後的圖像數據仍然通過 Sdram管理控製器返回 Sdram中保存。最後通過PCI橋把最終圖像返回到 PC機。

2.3 係統軟件的設計

本係統的控製流程相對簡單,因此在 Nioses II軟核中沒有內(nei) 嵌操作係統,而是通過IO操作調用中斷的方式實現運行狀態的控製、數據通信、協調外設等基本操作,控製係統各硬件模塊,使係統軟硬件協同工作。整個(ge) 係統搭建成功之後,在PC機上編寫(xie) 應用程序對整個(ge) SOPC係統的運行進行控製。

3 係統算法的具體(ti) 實現

3.1 濾波模塊

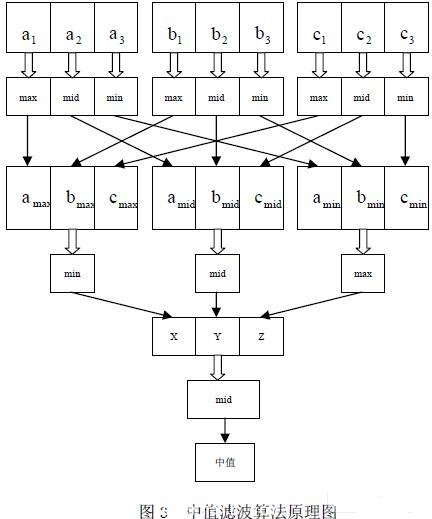

根據所采集到的圖像的特點,本文采用3×3的模板實現中值濾波,這種方法不僅(jin) 可以濾除圖像中的噪聲,而且可以將邊緣信息很好的保留下來。一般求取中值的方法是采用取冒泡法排序,但這種算法並不適合硬件實現。考慮到硬件實現的特點和效率,本文采用了一種全新的求取中值的算法,其原理如圖3所示。其中 max、mid、min分別表示三輸入的最大值、中值和最小值比較器。最後經幾輪比較後求得中值。

3.2 邊緣提取模塊及二值化模塊

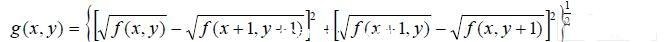

邊緣提取采用 Roberts算子。 Roberts邊緣檢測算子利用局部差分算子尋找邊緣,其計算由式 1給出。

由於(yu) 待處理圖像特征明顯,采用經驗閾值法對圖像進行二值化,算法簡單、實現方便。

3.3 邊緣細化模塊

本文的邊緣是建立在二值化之後的,因此處理的圖像都是二值化的,邊緣非常清晰,不需要太複雜的算法。這裏采用兩(liang) 個(ge) 3×3模板作乘積,如圖所示, X為(wei) 待處理像素。如果模板乘積不為(wei) 0,於(yu) 是中心象素為(wei) 1,反之為(wei) 0,即點的周圍有灰度為(wei) 0的象素,則保留此點,否則剔除。如此很容易得到二值化後點的單象素邊緣。

3.4 後續處理部分

後續處理部分由於(yu) 其數據處理量並不大且算法比較複雜,所以在本係統中,這部分算法在NiosesⅡ中以軟件的方法實現。由於(yu) 篇幅所限,在此不作詳細介紹。

4 係統測試結果的分析與(yu) 總結

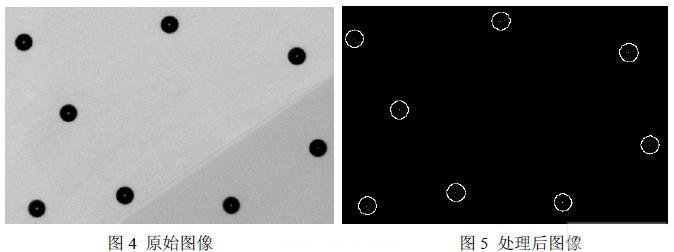

圖 4為(wei) 原始圖像。圖 5為(wei) 處理後的最終圖像,點中心已經標注如圖所示。

經測試,本係統所有算法用 C語言在 PC機(配置: Pentium( R) 4 CPU 3.00GHz, 512MB內(nei) 存)上實現,所需時間為(wei) 2'12",而本係統僅(jin) 需 30",其中主要耗時為(wei) NiosesII軟件處理部分,係統的硬件算法部分所耗時間不到 1"。

本文作者創新點:一是采用 FPGA設計硬件模塊實現圖像預處理算法,這是視覺測量係統在處理效率上的創新;二是在係統中加入Nioses II CPU,用以 FPGA難以實現的算法,從(cong) 而使基於(yu) SOPC技術的視覺測量係統更具靈活性,這是視覺測量係統在靈活性方麵的創新。基於(yu) 以上兩(liang) 點創新設計的視覺測量係統兼顧了效率和靈活性,為(wei) 視覺測量係統的設計和研究提供了一種新的思路。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們