大尺寸解決(jue) 方案

頂層封裝體(ti) 采用0.5 mm焊球節距,其尺寸逐漸超過12 × 12 mm,而且頂層焊球節距正逐步縮小到0.4 mm(圖3),在這樣的趨勢下,模塑型底層PoP逐漸得以應用。模塑型底層PoP也可以實現芯片疊層,包括將引線鍵合器件疊層在倒裝芯片上等情況。模塑型底層PoP以陣列的形式進行模塑處理,並類似傳(chuan) 統小節距球柵陣列(FBGA)封裝被切割分離,對應EMC能夠擴展到封裝邊緣,有助於(yu) 控製封裝的翹曲變形程度。

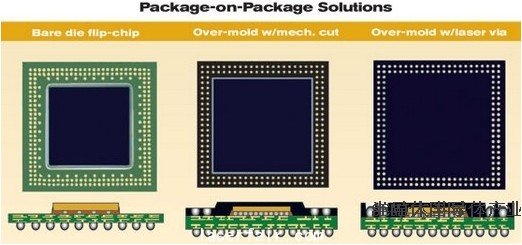

圖3. 存在多種窄互連節距PoP解決(jue) 方案,包括裸片型倒裝芯片方案、采用機械切割的模塑方案以及采用激光打孔的模塑方案。

一個(ge) 顯而易見的問題是如何暴露出頂層邊緣的焊盤,這樣才能通過焊球與(yu) 頂層封裝的互連。目前開發了兩(liang) 種方法實現這一目標,分別是機械切割和激光燒蝕。使用機械切割的方式,去除模塑之前,底層封裝上表麵邊緣焊球上覆蓋的EMC材料。這樣封裝邊緣的EMC厚度會(hui) 被降低,達到使焊球暴露以滿足頂層封裝回流的要求。必須嚴(yan) 格控製邊緣位置處EMC材料的高度或厚度,因為(wei) 這會(hui) 影響焊球的暴露直徑、暴露焊料量以及回流後與(yu) 頂層封裝的焊料融合質量。這種類型的底層PoP已經被開發出來,但還沒有廣泛應用於(yu) 生產(chan) 。

使用激光燒蝕暴露封裝上表麵邊緣焊球方法,在底層PoP中正獲得越來越多的關(guan) 注。激光燒蝕或激光鑽孔已經在封裝襯底製造中獲得了廣泛應用,而目前這一技術又被用於(yu) 在底層封裝上製作#p#分頁標題#e#EMC通孔。

同樣地,控製通孔製作對SMT過程中可以無缺陷地從(cong) 頂至底完成PoP回流至關(guan) 重要。通孔與(yu) 焊球的對準精度、模塑帽上部的外孔直徑(OHD)和暴露焊球的內(nei) 孔直徑都必須進行優(you) 化並嚴(yan) 格控製。目前已經在0.5 mm封裝間焊球節距和很多大尺寸(樣品尺寸)SMT試驗中顯示了所需加工能力,正在進行板級可靠性研究來探索可接受的DPM水平。對於(yu) 這種激光通孔型底層封裝,0.4 mm的封裝焊球節距正在開發中。

對於(yu) 0.4 mm的封裝互連焊球節距,翹曲變形必須控製在0.05 mm以下。激光通孔模塑技術與(yu) 低CTE襯底配合的方案已在開發階段。可以考慮使用裸片倒裝芯片底層PoP,但為(wei) 了適應0.4 mm封裝接口節距所需的更小封裝間距,倒裝芯片器件將會(hui) 需要被減薄到約0.06 mm,這樣對應的組裝高度約為(wei) 0.13 mm。對於(yu) 這麽(me) 薄的裸片倒裝芯片器件,如何操作和測試都將是棘手的問題。然而,裸片倒裝芯片PoP對應著最低的組裝成本。0.4 mm PoP接口節距的關(guan) 注熱點在於(yu) 選擇激光通孔的類型。一般認為(wei) ,通過開發和使用倒裝芯片模塑底部填充(MUF)以及其他低成本倒裝芯片方法,可以降低這種封裝的總體(ti) 成本。

未來的PoP

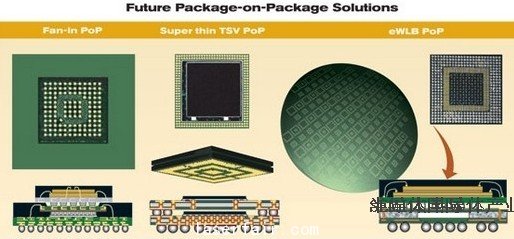

對於(yu) 小而薄PoP解決(jue) 方案的需求將會(hui) 繼續,預計#p#分頁標題#e#PoP將會(hui) 在目前市場份額的基礎上在其他低成本手機和其他消費設備中得以應用。為(wei) 滿足這些需求,正在開發使用更小PoP互連節距的更薄PoP解決(jue) 方案(圖4)。使用與(yu) 矽器件本身性質更加匹配的材料以降低翹曲變形,這種更薄的高密度襯底技術也在評估過程中。甚至使用包含穿透矽通孔(TSV)的矽基襯底方案以實現超薄PoP疊層也在考慮範圍內(nei) 。TSV可以實現高密度薄型存儲(chu) 器疊層,在不遠的將會(hui) 有可能會(hui) 在頂層PoP存儲(chu) 器疊層中得以使用。目前已經開發出扇入型PoP技術,實現高密度小節距封裝間互連(已經可以實現0.4 mm的頂層封裝節距)。

圖4. 未來的PoP解決(jue) 方案將會(hui) 實現更高互連密度、更薄體(ti) 積的疊層。

下一代三維扇出型圓片級封裝(FOWLP)技術,也就是被廣泛稱作嵌入性圓片級BGA(eELB)的封裝技術,可以實現超薄PoP模塊,正受到越來越多的關(guan) 注。這種eWLB封裝,在封裝的雙麵使用再布線層,並使用通孔穿透封裝邊緣處塑料扇出區域,可以實現約0.25 mm的封裝體(ti) 厚度,在封裝體(ti) 內(nei) 可以並排放置多個(ge) 芯片,而且可以實現節距小於(yu) 0.4 mm的高密度封裝接口,從(cong) 而可以允許小於(yu) 0.15 mm的封裝間隙。使用這種技術,可以實現高度低於(yu) 1.0 mm、尺寸小於(yu) #p#分頁標題#e#12 × 12 mm的封裝體(ti) 積。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們