1、半導體(ti) 製造:半導體(ti) 產(chan) 業(ye) 鏈中的王者

將半導體(ti) 產(chan) 業(ye) 鏈分為(wei) 上中下遊。上遊芯片製造封測支撐行業(ye) ,主要是半導體(ti) 設備和材料提供商,設備代表廠商有 ASML、應材、Lam,國內(nei) 企業(ye) 有北方華創、中微公司;材料代表廠商有信越化學、SUMCO、住友化學、陶氏化學,國內(nei) 廠商有華特氣體(ti) 、安集科技等。中遊半導體(ti) 製造產(chan) 業(ye) 分為(wei) 集成電路設計、製造、封測三個(ge) 部分。IC 設計廠商有高通、AMD、英偉(wei) 達、聯發科,國內(nei) 廠商有華為(wei) 海思、卓勝微、聖邦股份、紫光國微等;IC 製造廠商有台積電、聯電、格羅方德,國內(nei) 廠商有中芯國際、華虹半導體(ti) ;IC 封測廠商有日月光、矽品、AMKOR,國內(nei) 廠商有長電科技、華天科技、通富微電、晶方科技等。涵蓋 IC 設計、製造、封測三者的 IDM 廠商有 Intel、三星電子、索尼、TI,國內(nei) 廠商有長江存儲(chu) 和士蘭(lan) 微。半導體(ti) 下遊終端應用領域有汽車電子、工業(ye) 電子、通信、消費電子、PC 等領域。

在行業(ye) 價(jia) 值鏈中,半導體(ti) 製造占有近一半的產(chan) 值,毛利率也較高,但高價(jia) 值伴隨著高壁壘, 技術限製、高額的資本投入導致製造領域馬太效應十分明顯,龍頭廠商市占率和毛利率均遠高於(yu) 其他廠家。

2. 半導體(ti) 製造行業(ye) 三大核心問題

半導體(ti) 製造行業(ye) 的關(guan) 注點主要集中在三點上,這三個(ge) 問題是半導體(ti) 製造行業(ye) 技術發展的強勁推動力,也是馬太效應形成的根本原因:

半導體(ti) 製程的發展晶圓的尺寸晶圓廠的產(chan) 能我們(men) 將分別針對這三個(ge) 問題進行深度剖析。

2.1. 半導體(ti) 製程發展之路:摩爾定律還能走多遠?

半導體(ti) 製程工藝的發展,離不開摩爾定律。摩爾定律指出,當價(jia) 格不變時,集成電路上可容納的元器件的數目,約每隔 18~24 個(ge) 月便會(hui) 增加一倍,性能也將提升一倍。隨著晶體(ti) 管尺寸的減少,相同單位麵積中可以容納更多的晶體(ti) 管,相同大小的處理器可以獲得更高的處理能力。且小的晶體(ti) 管消耗的功率少,這減少了芯片的總功耗,產(chan) 生的熱量也隨之降低, 因此可以進一步提高時鍾速度。

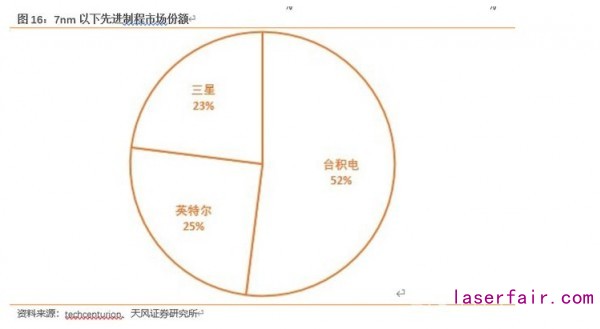

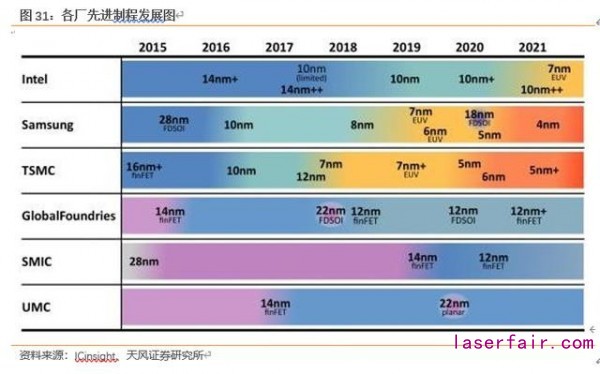

在製程發展上,Intel、IBM、三星、GF 等按著 180nm -> 130nm -> 90nm -> 65nm -> 45nm-> 32nm -> 22nm 的步調前行(三星和 GF 在 32nm 後轉向 28nm),而台積電等半導體(ti) 晶圓代工廠則走上了 150nm->110nm->80nm->55nm->40nm->28nm->20nm 的路線。隨著製程的發展,行業(ye) 集中度提升,10nm 以下製程隻有英特爾、三星、台積電三個(ge) 公司。

存儲(chu) 芯片製程發展與(yu) 邏輯芯片製程發展速度不太一致,但都受到摩爾定律的限製。DRAM 目前最先進工藝位於(yu) 18-15nm 之間,通常認為(wei) 10nm 是物理極限。從(cong) 2016 年開始,供應商開始采用 1xnm 節點製,其中供應商在路線圖上擁有三種 DRAM 產(chan) 品(1xnm,1ynm 和 1znm)。最初,將 1xnm 節點定義(yi) 為(wei) 具有 17nm 至 19nm 幾何形狀的 DRAM,1ynm 是 14nm 至 16nm,1znm 是 11nm 至 13nm。目前供應廠商的節點停留在 1xnm 狀態(1xnm, 1ynm,1znm,新三代製程包括 1anm,1bnm,1cnm 都屬於(yu) 1xnm 節點機製)。各大廠商正在積極尋找新的解決(jue) 方案,繼續擴展 DRAM 並提高性能,在未來的製程節點上可能會(hui) 使用 EUV 光刻實現轉變。SK Hynix 計劃在 1anm 使用 EUV,該技術將於(yu) 2021 年麵世。三星在 1znm 完成了對 DRAM 的 EUV 測試,但不會(hui) 用於(yu) 量產(chan) ,可能會(hui) 用於(yu) 1a 或 1b 的產(chan) 品中。美光則計劃將 193nm 浸沒式光刻和 SADP 擴展到 1bnm。

NAND 閃存驅動器的容量取決(jue) 於(yu) 芯片中的單元數量。在 2D NAND 結構中,存儲(chu) 單元在單個(ge) 管芯層中彼此相鄰放置,以提高存儲(chu) 容量。單元尺寸從(cong) 120 nm 減小到 1x nm,使容量增加了 100 倍,且當前 15nm/14nm 已經達到了極限。2D NAND 技術存在兩(liang) 個(ge) 局限,一是單元縮小是依靠光刻技術實現的,當光刻技術到達極限時,單元無法進一步縮小;二是當存儲(chu) 單元降至 20 nm 以下時,電荷從(cong) 一個(ge) 單元泄漏到另一個(ge) 單元的機會(hui) 大大增加,這種單元間幹擾會(hui) 導致數據損壞,從(cong) 而嚴(yan) 重損害閃存的可靠性。因此廠商們(men) 轉向 3D NAND, 單元以垂直堆疊的方式來增加密度。3D 堆疊有單層堆棧和線堆棧兩(liang) 種。在最新的 128 層中,廠商大多使用兩(liang) 個(ge) 64 層進行堆疊,三星計劃單層堆疊,在沒有其他新突破的情況下,128 層是單層堆疊的極限。而線堆疊在 500 層也可能存在問題,因此還需要探索新的堆疊方法。

不管是邏輯芯片還是存儲(chu) 芯片,製程量級越低,技術難度越大,製作成本也越高。IBS 的數據顯示:28nm 體(ti) 矽器件的設計成本大致在 5130 萬(wan) 美元左右,而 7nm 芯片需要 2.98 億(yi) , 5nm 則需要 5.42 億(yi) 美元,成本的增長速度越來越快。

半導體(ti) 製程以 28nm 為(wei) 界線,分為(wei) 先進製程和成熟製程。從(cong) 需求上看,先進製程需求在逐年增長,成熟製程需求較為(wei) 穩定。

2.1.1. 成熟製程——以 28nm 為(wei) 代表

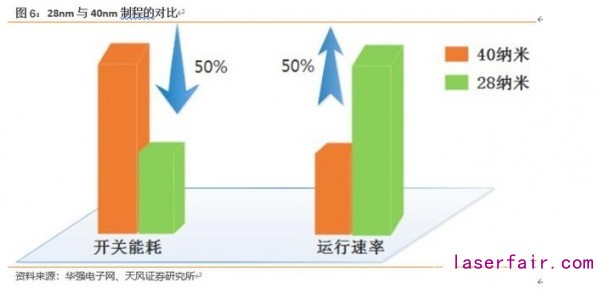

28nm 是半導體(ti) 製程裏性價(jia) 比最高、長周期屬性明顯的製程。一方麵,相較於(yu) 40nm 及更早期製程,28nm 工藝在頻率調節、功耗控製、散熱管理和尺寸壓縮方麵具有明顯優(you) 勢。另一方麵,由於(yu) 16nm/14nm 及更先進製程采用 FinFET 技術,維持高參數良率以及低缺陷密度難度加大,每個(ge) 邏輯閘的成本都高於(yu) 28nm,從(cong) 前麵製程成本比較的圖中也可以看出, 先進製程每一代成本都加速上升。隨著成本不斷上升,隻有少數客戶能夠負擔得起轉向高級節點的費用。

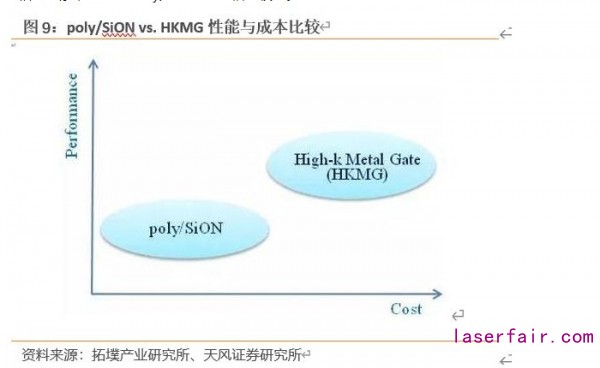

28nm 工藝處於(yu) 32nm 和 22nm 之間,業(ye) 界在 45nm 階段引入了 high-k 值絕緣層/金屬柵極(HKMG)工藝,在 32nm 處引入了第二代 high-k 絕緣層/金屬柵工藝,這些為(wei) 28nm 的逐步成熟打下了基礎。而在之後的先進工藝方麵,從(cong) 22nm 開始采用 FinFET(鰭式場效應晶體(ti) 管)等。28nm 正好處於(yu) 製程過渡的關(guan) 鍵點上,使其性價(jia) 比高。

28nm 製程主要有 HKMG 工藝(金屬柵極+高介電常數絕緣層 High-k 柵結構)和poly/SiON 工藝(多晶矽柵+氮氧化碳絕緣層的柵極結構)。與(yu) 傳(chuan) 統的 Poly/SiON 工藝相比, HKMG 技術可以有效的改善驅動能力,進而提高晶體(ti) 管的性能,同時大幅降低低柵極漏電量。Poly/SiON 工藝的特點是成本低,工藝簡單,適合對性能要求不高的手機和移動設備。HKMG 的優(you) 點是大幅減小漏電流,降低晶體(ti) 管的關(guan) 鍵尺寸從(cong) 而提升性能,但是工藝相對複雜,成本與(yu) Poly/SiON 工藝相比較高。

市場上提供 28nm 製程的主要廠商有台積電、聯電、三星、GF、中芯國際、華虹半導體(ti) 等。台積電於(yu) 2011 年開始導入 28nm 製程量產(chan) ,並在 2012 年攻克了 28nm HKMG 製程,三星則是在 2012 年實現了 28nm 的量產(chan) ,並於(yu) 2013 年導入了 28nm HKMG。UMC 在 2014 年實現量產(chan) 28nm 的 HKMG,目前公司放棄了 12nm 以下先進製程的研發。格芯在 2013 年量產(chan) ,格芯的主要工藝是 FD-SOI。中芯國際在 2015 年開始導入 28nm 製程量產(chan) 的, 並於(yu) 2018 年導入 HKMG,同年華虹宣布開始 28nm 製程量產(chan) 。

目前,雖然高端市場被 7nm、10nm 以及 14nm/16nm 工藝占據,但 40nm、28nm 等並不會(hui) 退出。 28nm~16nm 工藝現在仍然是台積電的營收主力,中芯國際則在持續提高28nm 良率。

在下遊需求方麵,IoT/穿戴裝置與(yu) 麵板驅動 IC 需求看漲。一方麵,IoT 芯片功能大多以數據收集為(wei) 主,功能單純且需維持長時間使用並兼顧低價(jia) 高量,因此多半集中在 28nm 以上的節點製造。近年 IoT 與(yu) 各項領域結合程度越來越高,5G 與(yu) AI 的推動讓 IoT 有了進一步的技術需求,也讓客戶評估製程技術轉移的可能性。另一方麵,受惠 OLED 麵板在更多的終端應用產(chan) 品上滲透率持續上升,以及國內(nei) OLED 廠商產(chan) 能陸續開出,OLED DDIC(麵板驅動 IC)市場也將成為(wei) 新一波 28nm 的成長動能;過去 OLED DDIC 以 40nm 製程為(wei) 主,但為(wei) 了滿足日後需求量上升,在既有 40nm 產(chan) 能已滿載而 28nm 產(chan) 能出現空缺的情況下,晶圓代工廠商也積極與(yu) 客戶合作製程轉移,期望能達到填補 28nm 缺口並囊括更多訂單。

2.1.2. 先進製程——得先進製程者得天下

半導體(ti) 從(cong) 成熟製程發展先進製程,必須要解決(jue) 光刻、晶體(ti) 管架構、溝道材料三個(ge) 問題。

光刻

光刻是半導體(ti) 製造過程中最難的一步。在半導體(ti) 製作過程中,光刻設備會(hui) 投射光束, 穿過印著圖案的掩模及光學鏡片,將線路圖曝光在帶有光感塗層的矽晶圓上;通過蝕刻曝光或未受曝光的部份來形成溝槽,然後再進行沉積、蝕刻、摻雜,架構出不同材質的線路; 此製程被一再重複, 就能將數以十億(yi) 計的 MOSFET 或其他晶體(ti) 管,建構在矽晶圓上,形成一般所稱的集成電路。光刻決(jue) 定了半導體(ti) 線路的精度,以及芯片功耗與(yu) 性能,相關(guan) 設備需要集成材料、光學、機電等領域最尖端的技術。

光源是光刻機核心之一,光刻機的工藝能力首先取決(jue) 於(yu) 其光源的波長。光源波長越短,激發出的更小尺寸的光子。曝光方式分為(wei) Stepper 和 Scanner 兩(liang) 種。Stepper 一次性將整個(ge) 區域進行曝光;Scanner 將鏡頭沿 Y 方向的一個(ge) 細長空間曝光,矽片和掩模同時沿 X 方向移動經過曝光區動態完成整個(ge) 區域的曝光。Scanner 曝光圖像畸變小、一致性高,速度也更快,所以目前主流光刻機都是 Scanner。

下一代的工藝,就必須采用 EUV 光源的設備,三星 7nm 節點上已經采用了 EUV 設備。隨著先進製程的進一步發展,EUV 光刻設備是必要設備。

目前 EUV 技術主要運用在邏輯工藝製程中。由於(yu) 三星、台積電在 2019 年大規模量產(chan) EUV 工藝,所以 2019 年是 ASML 的 EUV 光刻機大幅增長的一年。ASML 2019 年財報顯示,全年共計出貨 26 台 EUV 光刻機,營收 118.2 億(yi) 歐元,同比增長了 8,EUV 光刻機的營收占比從(cong) 2018 年的 23 提升到 31 。未來也會(hui) 保持這個(ge) 趨勢,預計 2020 年交付 35 台 EUV 光刻機,2021 年則會(hui) 達到 45 台到 50 台的交付量。ASML 還針對後續更為(wei) 先進的 3 納米、2 納米製程的需求,開始規劃新一代 EUV 光刻機 EXE:5000 係列。

晶體(ti) 管架構

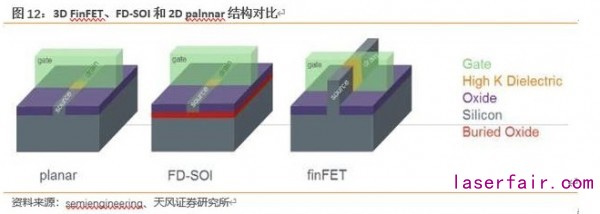

在半導體(ti) 製程進化的過程中,um 級及高尺寸 nm 級采用的都是 MOS 結構,縮小尺寸就是縮小了柵極橫向的寬度。隨著製程要求的進一步提高,如果采用 MOS 結構,線寬需要繼續縮小,這會(hui) 造成源端和漏端短路,電路會(hui) 因此失效,且飽和電流會(hui) 過小。

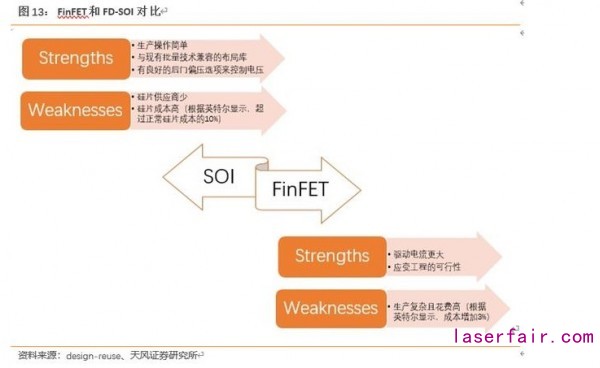

為(wei) 了解決(jue) 這些問題,出現了 FinFET 技術和 FD-SOI 技術。

FinFET 是一種場效應晶體(ti) 管,其具有一從(cong) 基材突出的狹窄半導體(ti) 材料有源區域,因此, 類似於(yu) 鰭(fin)。此鰭包括源極區域與(yu) 漏極區域。鰭的有源區域通過淺溝槽隔離(shallow trench isolat1n, STI)而被分隔,一般通過二氧化娃(S12)。鰭式場效應晶體(ti) 管也包括一位於(yu) 源極區域與(yu) 漏極區域之間的柵極區域。柵極區域形成於(yu) 鰭的上表麵與(yu) 側(ce) 壁,以包裹圍繞鰭。在柵極下方延伸且介於(yu) 源極區域與(yu) 漏極區域之間的鰭的部分為(wei) 溝道區域。

FD-SOI 技術是一種平麵工藝,利用不同的起始襯底,利用現有的 CMOS 平麵製造方法的性能並擴展其性能。FD-SOI 襯底具有一層超薄的絕緣體(ti) 層掩埋氧化物,位於(yu) 基底矽的頂部。晶體(ti) 管通道由非常薄的矽薄膜組成。在設計上,FD-SOI 技術比傳(chuan) 統的大體(ti) 積 CMOS 具有更好的晶體(ti) 管靜電特性,並減少了器件泄漏。

SOI 技術不需要在 Fab 廠上進行大量投資,且具有良好的背柵偏置選項。通過在 BOX 下方創建後柵極區域,我們(men) 還可以控製電壓,這使其適用於(yu) 低功耗應用。但 SOI 技術很難控製晶片中的錫矽膜,故晶片的成本要高於(yu) 塊狀矽晶片,且 SOI 晶圓的供應商數量比較少, 這將使總工藝成本增加約 10%。與(yu) SOI 相比,FinFET 具有更高的驅動電流,應變技術可用於(yu) 增加載流子遷移率,但 FinFET 製造工藝複雜。

在應用上,FinFET 主要應用於(yu) 高性能、高集成度領域,比如 GPU 和 CPU 等高性能器件。

FD-SOI 在 IoT、5G、AI 和 ADAS/自動駕駛中在成本和性能方麵顯現出優(you) 勢。

兩(liang) 種技術各有特點,未來在 40/28 納米,14/10 納米的 FD-SOI 和 FinFET 技術會(hui) 共存一段相當長時間。最終發展到 7 納米及以下時,SOI 也將從(cong) 2D 發展到 3D,即發展為(wei) SOI FinFET 工藝。這表明 SOI 與(yu) FinFET 技術可能殊途同歸。

溝道材料

溝道是連接MOS 器件源和漏之間的一個(ge) 導電區域,溝道材料影響電子在溝道中的遷移率。半導體(ti) 製程向更先進的節點邁進時,需要找到合適的溝道材料,加快電子在溝道中的移動速度,提高器件的頻率。鍺及 III-V 族化合物具有這種特性,但是這些材料必須要具備與(yu) 矽材料兼容的工藝,因此目前 SiGe 是比較好的選擇。

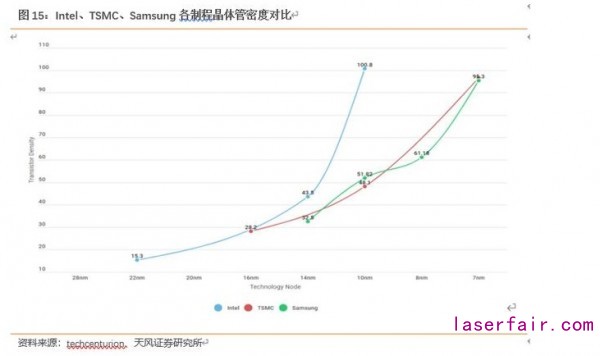

隨著這三個(ge) 問題的解決(jue) ,半導體(ti) 製程向先進工藝發展。目前,台積電和三星均已有 7nm 工藝,英特爾為(wei) 10nm 工藝,但從(cong) 晶體(ti) 管密度上看,英特爾 10nm 技術可與(yu) 三星和台積電的 7nm 技術媲美。

先進製程的優(you) 勢在哪裏?

從(cong) 客戶端來看,目前選擇 7nm 工藝的客戶已經超過 10 多家(AMD、蘋果、Bitman、博通、海思、聯發科、英偉(wei) 達、高通、賽靈思、平頭哥等),7nm EUV 至少有 5 家(AMD、蘋果、海思、三星、高通),6nm 的客戶則除了以上的 5 家之外,還多了博通和聯發科,5nm 目前已確認將采用的客戶則有 AMD、蘋果、海思、三星和賽靈思。這些客戶帶來龐大體(ti) 量的訂單給代工廠帶來高額營收,2019年,台積電作為(wei) 唯一采用 7nm 工藝技術的純晶圓代工廠,每片晶圓營收顯著增加。

除了晶圓代工和邏輯芯片製造外,三星、美光、SK Hynix 和 Kioxia/WD 等存儲(chu) 器供應商也在使用先進的工藝製造 DRAM 和 flash 存儲(chu) 器組件。下遊企業(ye) 采用越來越先進的工藝, 未來先進製程會(hui) 給製造廠商貢獻更多的營收。

2.2. 晶圓尺寸

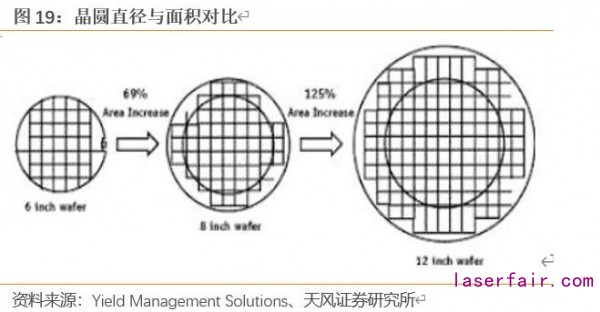

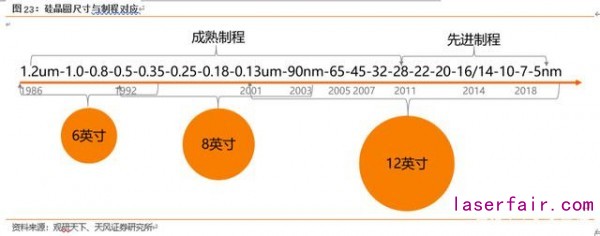

從(cong) 晶圓發展曆程來看,晶圓尺寸經曆了 2 英寸、4 英寸、5 英寸、6 英寸、8 英寸和 12 英寸。晶圓的尺寸越大,在單片晶圓上製造芯片的數量就越多,單片芯片的分攤成本隨之降低,並且晶圓片邊緣的損失會(hui) 減小,因此發展大尺寸晶圓片有利於(yu) 降低成本,但同時對設備和工藝的要求也越高。在同樣的工藝條件下,300mm 半導體(ti) 晶圓的可使用麵積超過200mm 晶圓的兩(liang) 倍以上,可使用率(衡量單位晶圓可生產(chan) 的芯片數量的指標)是 200mm 矽片的 2.5 倍左右。圖 19 為(wei) 不同尺寸晶圓麵積對比,資料來源於(yu) 文章 Critical Dimension Sample Planning for 300 mm Wafer Fabs(作者:Sung Jin Lee, Raman K. Nurani, Ph.D., Viral Hazari, Mike Slessor, KLA-Tencor Corporation, J. George Shanthikumar, Ph.D., UC Berkeley)。

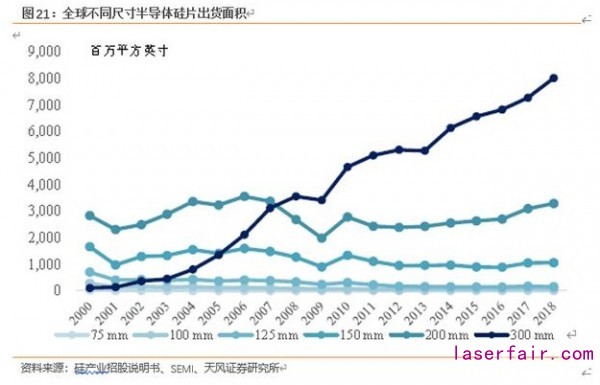

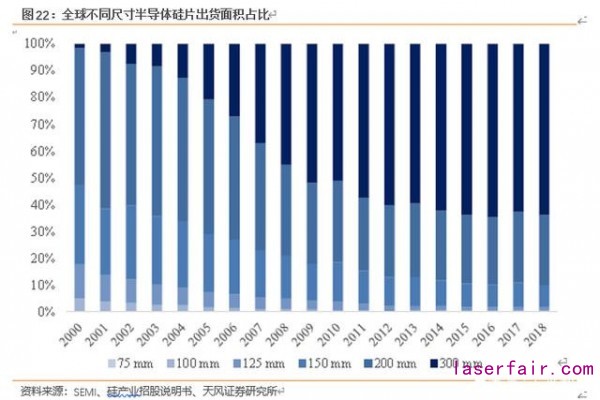

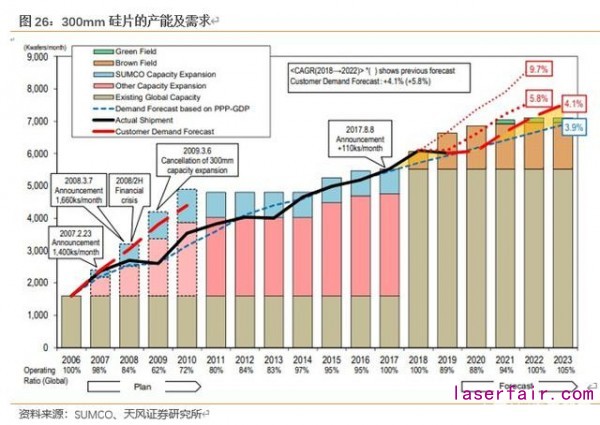

晶圓的原材料就是矽片,晶圓尺寸、需求與(yu) 矽片息息相關(guan) 。全球半導體(ti) 矽片市場最主流的產(chan) 品規格為(wei) 300mm 和 200mm,300mm 矽片出貨麵積增長速度明顯高於(yu) 200mm 和150mm。2018 年,300mm 矽片和 200mm 矽片市場份額分別為(wei) 63.83 %和 26.14% ,兩(liang) 種尺寸矽片合計占比接近 90%。

200mm 矽片的發展:

200mm 矽片的發展:2011 年開始,200mm 半導體(ti) 矽片市場占有率穩定在 25-27%之間。2016 年至 2017 年,由於(yu) 汽車電子、智能手機用指紋芯片、液晶顯示器市場需求快速增長,200mm 矽片出貨麵積同比增長 14.68% 。2018 年,受益於(yu) 汽車電子、工業(ye) 電子、物聯網等應用領域的強勁需求,以及功率器件、傳(chuan) 感器等生產(chan) 商將部分產(chan) 能從(cong) 150mm 轉移至200mm,帶動 200mm 矽片繼續保持增長。

300mm 矽片的發展:自 2000 年全球第一條 300mm 芯片製造生產(chan) 線建成以來,300mm 半導體(ti) 矽片市場需求增加,出貨麵積不斷上升。2008 年,300mm 半導體(ti) 矽片出貨量首次超過 200mm 半導體(ti) 矽片;2009 年,300mm 半導體(ti) 矽片出貨麵積超過其他尺寸半導體(ti) 矽片出貨麵積之和。2000 年至 2018 年,由於(yu) 移動通信、計算機等終端市場持續快速發展,300mm 半導體(ti) 矽片市場份額從(cong) 1.69 大幅提升至 63.83% ,成為(wei) 半導體(ti) 矽片市場最主流的產(chan) 品。2016-2018 年,由於(yu) 人工智能、區塊鏈、雲(yun) 計算等新興(xing) 終端市場的蓬勃發展,300mm 半導體(ti) 矽片出貨麵積年均複合增長率為(wei) 8.36 %。

製程工藝的進步對矽片麵積要求更高。目前,90nm 及以下的製程主要使用 300mm 矽片, 90nm 以上的製程主要使用 200mm 或更小尺寸的矽片。隨著半導體(ti) 製程的不斷縮小,芯片生產(chan) 的工藝愈加複雜,生產(chan) 成本不斷提高,成本因素驅動矽片向著大尺寸的方向發展。因此未來幾年,300mm 仍將是半導體(ti) 矽片的主流品種。

下遊產(chan) 品中,大尺寸矽片能夠生產(chan) 更多類型的產(chan) 品,且尺寸越大,高端芯片需求越高。不過近年來受到新興(xing) 市場的驅動,八寸晶圓也麵臨(lin) 供不應求的局麵。全球 8 英寸晶圓廠大多擁有成熟的製程,運營時間較長從(cong) 而可以讓固定成本和運營成本降低,適合多樣化產(chan) 品和特色工藝的開發。

2.3. 晶圓產(chan) 能

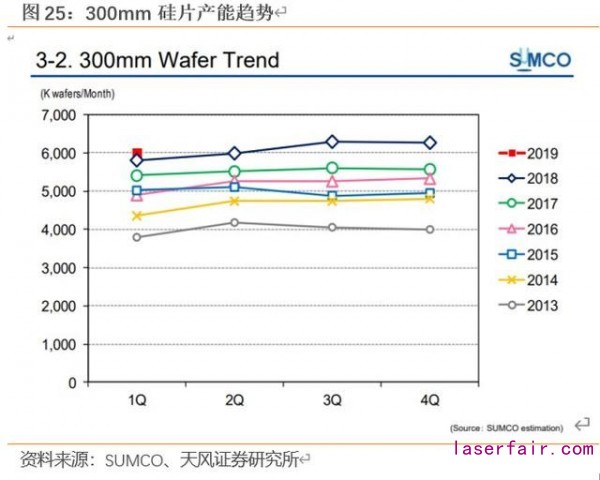

自 2000 年以來,半導體(ti) 產(chan) 業(ye) 靠著增加晶圓投片量來提高芯片出貨量,利用製程微縮讓每片晶圓切割出更多芯片的貢獻並不多。從(cong) 2000~2019 年,每片晶圓切割出的良品芯片的年平均成長率僅(jin) 0.9%,但通過增加晶圓投片來增加的良品芯片的年平均成長率達 6.5%。總體(ti) 來看,2000~2019 年全球每年新增加的芯片數量,有 86%來自晶圓投片量增加,隻有 14%是來自製程微縮讓每片晶圓切割出更多芯片。因此晶圓產(chan) 能意味著潛在的銷售量, 是影響製造廠商營收的一大因素。

從(cong) 供需結構分析,供給端 2019Q4 矽片全球產(chan) 能,200mm 已經回落至 500 萬(wan) 片/月,同2016 年周期啟動時同一水準,300mm 接近 600 萬(wan) 片/月,落於(yu) 景氣高點水位之下,考慮到需求端芯片存在 1 高性能計算芯片/指紋識別 die 麵積增大;2 新應用(5G/車聯網/雲(yun) 計算)等所需矽含量提升,供需緊平衡已經出現。

根據製程節點劃分,200mm 當量晶圓月產(chan) 能如下所示。先進製程的發展是晶圓需求的強勁拉動力。

截至 2019 年 12 月,全球排名前五名晶圓每月的產(chan) 能超過 100 萬(wan) 片晶圓(200mm 等效晶圓),產(chan) 能合計占全球晶圓總產(chan) 能的 53%。

2017 至 2020 年,全球芯片製造產(chan) 能(折合成 200mm)預計將從(cong) 1985 萬(wan) 片/月增長至2407 萬(wan) 片/月,年均複合增長率 6.64 ;中國芯片製造產(chan) 能從(cong) 276 萬(wan) 片/月增長至 460 萬(wan) 片/月,年均複合增長率 18.50 。近年來,隨著中芯國際、華力微電子、長江存儲(chu) 、華虹宏力等中國大陸芯片製造企業(ye) 的持續擴產(chan) ,中國大陸芯片製造產(chan) 能增速高於(yu) 全球芯片產(chan) 能增速。

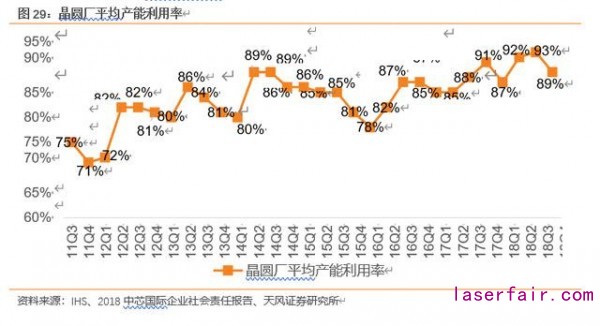

從(cong) 產(chan) 能利用率方麵看,晶圓廠平均產(chan) 能利用率略有波動,但整體(ti) 呈現上升趨勢。

3. 半導體(ti) 製造行業(ye) 競爭(zheng) 邏輯

半導體(ti) 製造行業(ye) 具有人才、技術和資本密集的特點。

人才和技術密集:半導體(ti) 製造行業(ye) 是受研發和技術驅動的行業(ye) ,對人才和技術極為(wei) 看重。2018 年畢馬威聯合 SEMI 發布了一份問卷調查數據,受訪者皆為(wei) 全球半導體(ti) 的行業(ye) 高管,其中有 64%的人認為(wei) 人才風險是三大運營風險之一。集成電路人才稀缺,《中國集成電路產(chan) 業(ye) 人才白皮書(shu) (2018-2019 年版)》預計中國 IC 製造行業(ye) 人才 2021 年需求達到 24.6 萬(wan) ,比 2019 年多 10.2 萬(wan) ,因此半導體(ti) 行業(ye) 成為(wei) 了國內(nei) 引進人才最多的行業(ye) 。中芯國際引進梁孟鬆,紫光集團旗下的長江存儲(chu) ,以及合肥長鑫的 DRAM 廠引進美光、SK 海力士等大廠的人才。在引進人才之後,中芯國際在 19 年底成功實現 14nm 量產(chan) ,長江存儲(chu) 量產(chan) 了 64 層堆棧 3D 閃存,合肥長鑫量產(chan) 了 DDR4 內(nei) 存。

在技術方麵,在上文已經介紹過各大公司在製程方麵的發展,以及先進製程對公司營收的貢獻。從(cong) 曆史的發展看,當某家大廠可以量產(chan) 最新先進製程時,公司的訂單量會(hui) 飆升,營收也會(hui) 大漲。

資本密集:半導體(ti) 製造廠商需要持續不斷投入工藝製程和產(chan) 品結構的研發,且半導體(ti) 製造企業(ye) 是重資產(chan) 企業(ye) ,需要資本的大力支持。自 1990 年代以來,半導體(ti) 行業(ye) 在研發強度方麵一直領先於(yu) 所有其他主要工業(ye) 領域,每年用於(yu) 研發的支出平均約占總銷售額的 15%,近幾年略有下降,是因為(wei) 收入端增長更強勁。雖然半導體(ti) 行業(ye) 過去五年研發支出年度增長放緩,但是由於(yu) 先進製程的發展對技術提出了更高的需求,包括 EUV 光刻技術、sub-3nm 工藝技術、3D 模具堆疊技術使未來五年研發支出會(hui) 加速增長, 預計 2019-2024 年複合增長率為(wei) 4.4 %。

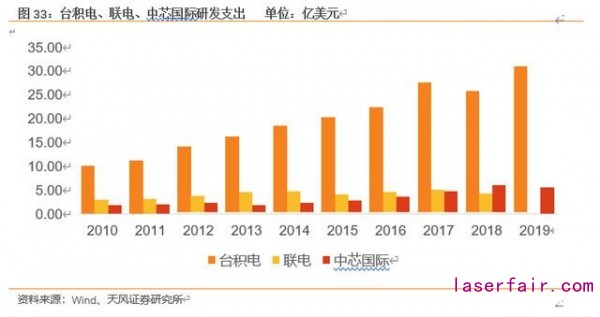

以晶圓代工廠為(wei) 例,台積電和中芯國際研發支出略有波動,整體(ti) 呈現上升趨勢。聯電在放棄 7nm 製程研發後,研發支出略有下降。

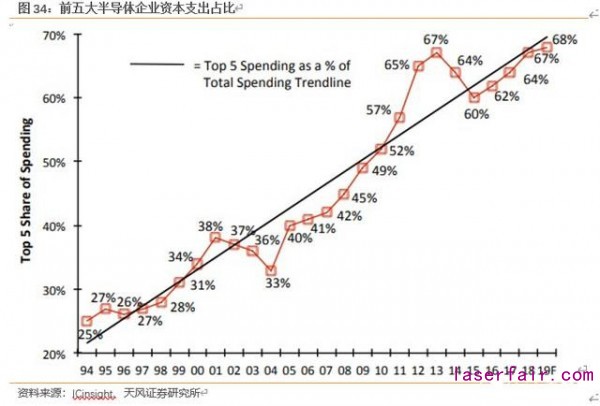

在資本支出方麵,前五大公司(三星、英特爾、台積電、SK Hynix 和美光)資本支出總額占全球半導體(ti) 行業(ye) 資本支出的 68%,創曆史新高。

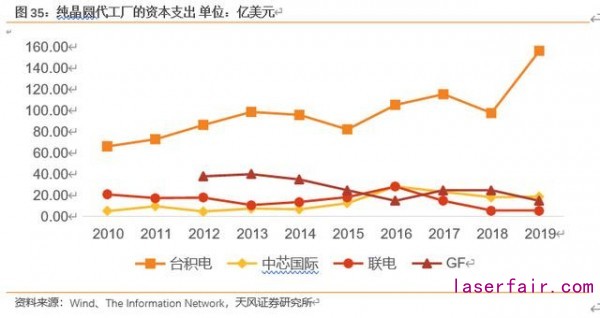

單看純晶圓代工廠,台積電、中芯國際、聯電、格芯資本支出均在全球純晶圓代工廠前列。台積電飛速上升,其中台積電 19 年資本支出同比增長 61.6 %。中芯國際在這兩(liang) 年略有下降,但相較 15 年前依舊處於(yu) 較高水平。聯電在放棄 7nm 製程的研發後,資本支出近兩(liang) 年有明顯下降。格芯雖然放棄了 7nm 製程,但是轉戰 SOI 工藝,因此資本支出下降沒有聯電明顯

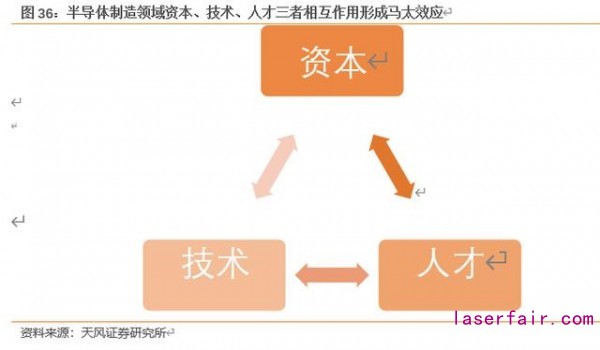

綜上,半導體(ti) 製造行業(ye) 發展靠的是人才、技術、資本三者結合。人才是企業(ye) 的軟實力, 為(wei) 公司提供源源不斷的研發智慧。半導體(ti) 製造行業(ye) 是重資產(chan) 行業(ye) ,先進製程的進步與(yu) 先進設備有關(guan) ,資本的投入為(wei) 先進技術研發、廣羅人才提供支持。技術發展是企業(ye) 成為(wei) 行業(ye) 龍頭的必要標準。反向看,技術發展會(hui) 為(wei) 公司開拓廣闊市場,營收增長,實現資本積累,提高公司實力,產(chan) 生規模效應,吸引人才流入。三者相互作用,使半導體(ti) 龍頭企業(ye) 技術發展越來越快,資本積累越來越多,同樣擁有專(zhuan) 業(ye) 技術的人才也越多, 馬太效應由此形成

4. 製造行業(ye) 長期成長邏輯/未來增量空間

半導體(ti) 製造行業(ye) 的發展是受到下遊需求驅動的,因此對下遊市場的發展進行分析能夠理清製造行業(ye) 的長期成長邏輯及未來的增量空間。

4.1. 長期成長邏輯

將應用分為(wei) 兩(liang) 類,一類是受到摩爾定律主導的市場,主要包括智能手機、電腦和服務器的CPU 和存儲(chu) 芯片;一類是超越摩爾定律的應用領域,主要包括模擬芯片、傳(chuan) 感器、功率芯片等領域。

受摩爾定律主導的市場

摩爾定律主導的市場是半導體(ti) 市場的主戰場,從(cong) 市場增速來看,存儲(chu) 芯片、邏輯芯片增速依舊排在前列。

CPU 為(wei) 了滿足高性能計算、續航散熱這些需求,對芯片製程需求越來越高,手機和電腦都是最先采用先進製程的領域。從(cong) 性能上看,據 techcenturion 評測,目前手機 CPU 芯片性能最好的是蘋果的 A13,采用的是台積電的 7nm 工藝。

目前性能最高的 PC CPU 芯片為(wei) AMD 的銳龍 Thread Ripper 3990X,采用的也是台積電的7nm 工藝。

從(cong) 手機和電腦的 CPU 芯片發展中可以看到搶占最先進製程的重要性。存儲(chu) 芯片的發展前麵也已經提過了,市場被擁有先進製程的大廠商三星、海力士、美光等瓜分。

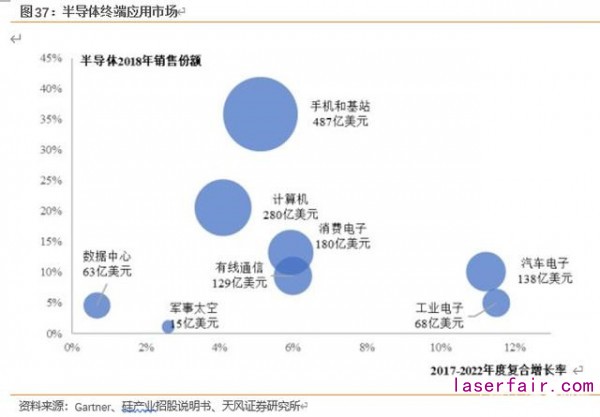

CPU 和存儲(chu) 器的長期動能來自手機、PC 和服務器的增長。目前手機、計算機等仍是半導體(ti) 行業(ye) 終端最大的應用市場。2018 年全球手機和基站、計算機用芯片銷售額分別為(wei) 487 億(yi) 美元、280 億(yi) 美元,在半導體(ti) 終端市場的占比分別為(wei) 36%、21% 。智能手機和計算機市場是摩爾定律前進的推動力。

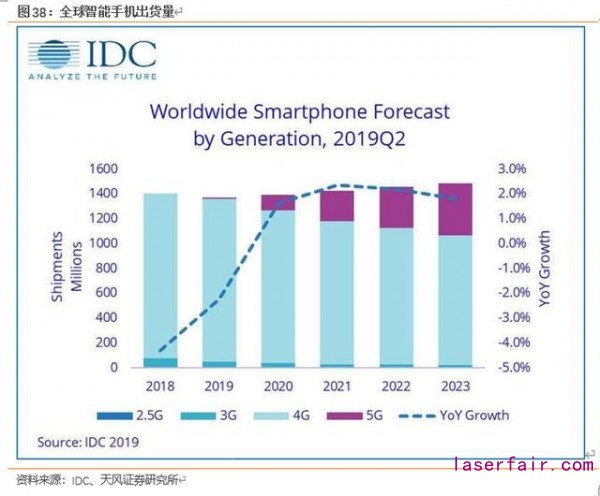

智能手機的成長動力主要源自 5G 的出現。2020 年是 5G 開始興(xing) 起的一年,IDC 預計 2020 年將出貨 1.9 億(yi) 部 5G 智能手機,占智能手機總出貨量的 14%,預計到 2023 年,這一數字將增長到全球智能手機出貨量的 28.1%。

2019 年全球 PC 出貨量同比增長 2.7%,這是自 2011 年市場增長 1.7%以來,PC 首次實現全年增長,這也是 PC 市場進入回暖的明顯跡象。盡管市場麵臨(lin) 挑戰,PC 市場一直被看衰, 但是可以看到 PC 需求仍然一直存在。從(cong) PC 的設計上看,全麵屏和輕薄化是趨勢,性能、續航、散熱需求也逐漸增加,這些需求對電腦 CPU 的要求更高。

數據的高速增長帶動了數據中心業(ye) 務急速增長。MarketsandMarkets 估計,到 2024 年,全球數據中心機架服務器市場將從(cong) 2019 年的 521 億(yi) 美元增長到 1025 億(yi) 美元,在預測期內(nei) 複合年增長率(CAGR)為(wei) 14.5 %。推動市場增長的因素是對可擴展數據中心和高密度計算的需求。此外,邊緣計算、物聯網和雲(yun) 計算等新興(xing) 技術的進步有望為(wei) 數據中心機架式服務器供應商創造充足的機會(hui) 。

從(cong) 邏輯芯片的營收變化看,邏輯芯片營收占比一直處於(yu) 25 左右,多年占比穩定,據 WSTS估計,19 年營收 1046 億(yi) 美元,較 18 年有下降,但是占比提升,因此營收主要受半導體(ti) 整體(ti) 行業(ye) 景氣度的影響,而 20 年營收會(hui) 有所上升,占比也有提升。

在半導體(ti) 各類芯片中,存儲(chu) 芯片在營收中占比最大。存儲(chu) 芯片市場 2018 年營收 1579.67億(yi) 美元,占比 33.70% ,在整個(ge) 半導體(ti) 市場的份額已超過 1/3。根據 WSTS 19 年 11 月公布的預測,2019 年占比有所下降,約為(wei) 25.89 %,但仍然是占比最大的板塊。從(cong) 增長率看, NAND 產(chan) 能和價(jia) 格的增長會(hui) 高於(yu) DRAM。

長遠來看,邏輯芯片和存儲(chu) 芯片的增量市場來自於(yu) 5G、雲(yun) 計算、AI 和物聯網,數據種類、數量高速的增長,對處理器的要求越來越高,對存儲(chu) 的需求也在增大,因此摩爾定律的主導市場發展空間大,利潤率高,依舊是各大廠商競相追逐的領域。

對於(yu) 半導體(ti) 製造廠商而言,目前 CPU 和存儲(chu) 領域是製造龍頭蠶食的區域,擁有先進製程的製造公司才有能力加入這個(ge) 市場。且手機、PC 經過多年的發展基本上屬於(yu) 穩定的存量市場,因此為(wei) 了爭(zheng) 奪市場份額,各大廠商在製程上追逐。除此之外,製造廠商迅速布局 5G、雲(yun) 計算、AI 和物聯網提供的新的增量市場。由於(yu) 先進製程研發的穩步推進,台積電一直是蘋果的代工,而高通的訂單則一直被三星和台積電爭(zheng) 奪,技術是設計廠商選擇代工的影響因素,因此想要在摩爾定律主導的市場獲取市場份額,持續實現成長,製造廠商第一要務是推動自身先進製程的發展。

超越摩爾定律應用領域

摩爾定律的推進降低了 CPU、存儲(chu) 、邏輯芯片的成本,但是不能給模擬芯片、傳(chuan) 感器芯片、射頻芯片等帶來理想的成本效益。RF、電源管理、MEMS、CMOS 傳(chuan) 感器等芯片需要更專(zhuan) 業(ye) 化,需要通過集成增加更多功能。雖然這些專(zhuan) 用芯片的製造商仍然關(guan) 注尺寸、速度和功率,但是不一定需要在最先進的節點上進行功能集成,它們(men) 需要綜合考慮性能、集成度和成本。這類應用統稱為(wei) 超越摩爾定律的應用領域。摩爾製程主導的領域追求的是製程的發展,而超越摩爾定律的應用領域朝著多樣化發展。

物聯網應用就是一個(ge) 很好的例子。典型的物聯網設備可能包括具有模擬接口的傳(chuan) 感器、用於(yu) 編碼和數據存儲(chu) 的存儲(chu) 器、用於(yu) 數據通信的射頻功能、用於(yu) 控製設備和處理數據的處理器,另外可能還有電池和電池接口。大多數情況下,這些設備可能處於(yu) 休眠模式,所以超低漏電是一個(ge) 關(guan) 鍵要求。然而,一旦被信號喚醒,設備必須立即切換到高性能模式,以便在存儲(chu) 器中獲取或存儲(chu) 數據,處理數據,然後傳(chuan) 輸或接收數據。7nm 邏輯芯片在處理這些不同功能方麵沒有任何實際優(you) 勢。還有雲(yun) 計算和數據中心的人工智能推理/訓練應用與(yu) 芯片製程關(guan) 係不大,其最大的問題是功耗。

根據 Yole 統計,2017 年超越摩爾的應用領域對晶圓需求為(wei) 4500 萬(wan) 片(8 英寸當量),預計到 2023 年需求會(hui) 增長到 6600 萬(wan) 片,CAGR 10 。

1. 電源管理芯片

Yole 預測電源 IC 將受益於(yu) 多個(ge) 主要終端市場的擴張而在 2016~2022 年期間獲得 3.6%的複合年增長率,與(yu) 半導體(ti) 整體(ti) 產(chan) 業(ye) 的增長趨勢保持一致。2016 年,電源 IC 市場的規模預計為(wei) 145 億(yi) 美元,到 2022 年預計將增長至 180 億(yi) 美元。

電源管理芯片在電子產(chan) 品市場舉(ju) 足輕重,幾乎所有的電子產(chan) 品和設備都需要電源管理芯片。通信是最主要的電源管理芯片市場,主要包括智能手機市場和通信基站市場,而這兩(liang) 部分 市場都受益於(yu) 5G 的發展,智能手機出貨量及單部手機電源管理芯片數量或有增長,5G 基站建設量大幅增長,單個(ge) 基站通道數增加,這些都讓通信市場成為(wei) 當下有潛力的增量市場。汽車電源管理芯片受益於(yu) 新能源汽車的驅動;消費電子市場受到物聯網發展的驅動,下遊 應用持續分散化,不同應用對電源管理的要求也不同,TWS 耳機的發展是目前電源管理芯片最明顯的消費電子增長點,由於(yu) TWS 耳機體(ti) 積小需要集成度更高的電源管理芯片,且其充電盒也拉動了電源管理芯片的需求。隨著工業(ye) 從(cong) 規模化走向自動化、智能化,工業(ye) 與(yu) 信息化的深度融合、智能製造轉型升級將帶動工業(ye) 電子電源管理芯片需求的增長。

2. 傳(chuan) 感器芯片

傳(chuan) 感器領域,手機攝像頭的需求帶動 CMOS 圖像傳(chuan) 感器增長迅速;自動駕駛技術的快速發展,增加了對圖像傳(chuan) 感器、MEMS 傳(chuan) 感器、激光雷達、超聲波傳(chuan) 感器多種類型傳(chuan) 感器的需求。VR/AR 帶動 MEMS 傳(chuan) 感器需求增長。

電源管理芯片、傳(chuan) 感器芯片等對芯片製程要求沒有那麽(me) 苛刻,因此除了龍頭廠商外,其他半導體(ti) 製造廠商也能分一杯羹,格芯、聯電、中芯國際、華虹半導體(ti) 等在這些細分領域都能擁有一定市場。之前格芯和聯電都宣布了放棄研發 7nm 工藝,把更多的精力放在了專(zhuan) 用芯片的製造商。因此,各大廠商如果在製程競爭(zheng) 上沒有優(you) 勢,可以抓住這類市場的機會(hui) , 進行專(zhuan) 用芯片的研發。

4.2. 近年來的主線,5G、IoT、車用半導體(ti) 、AI 提供大增量(略)

前麵介紹製造廠商的兩(liang) 個(ge) 市場時,提到 5G、IoT、車用半導體(ti) 、AI 等新興(xing) 領域給這些市場注入了新的發展動力,這也是近年來半導體(ti) 領域應用的主線。

5. 中國半導體(ti) 製造業(ye) 的機會(hui) 在哪裏?

目前,中國半導體(ti) 行業(ye) 還處在初期發展階段,國內(nei) 企業(ye) 長期研發投入和積累不足,使我國半導體(ti) 行業(ye) 在國際分工中多處於(yu) 中低端領域,高端產(chan) 品市場被歐美日韓台等少數國際大公司壟斷。我國半導體(ti) 產(chan) 業(ye) 亟待解決(jue) 的兩(liang) 個(ge) 問題是:供需失衡和結構失衡。

供需失衡

中國是全球最大的半導體(ti) 消費市場,也是全球工業(ye) 製造中心,人口基數決(jue) 定了半導體(ti) 終端產(chan) 品的消耗量。盡管中國半導體(ti) 產(chan) 業(ye) 銷售規模持續擴張,但本地製造商隻能滿足該國約 30%的需求,因此隻能長期依賴於(yu) 進口。根據中國半導體(ti) 行業(ye) 協會(hui) 統計,2018 年,中國集成電路進口金額達 3120.6 億(yi) 美元。中國半導體(ti) 產(chan) 業(ye) 國產(chan) 化進程嚴(yan) 重滯後於(yu) 國內(nei) 快速增長的市場需求,中國半導體(ti) 供需失衡嚴(yan) 重,國內(nei) 企業(ye) 進口替代空間非常可觀。

結構失衡

國內(nei) 半導體(ti) 行業(ye) 結構失衡。大多數半導體(ti) 公司都是定位於(yu) 中低端市場的中小半導體(ti) 設計公司,大規模、技術壁壘高的製造公司比較少。從(cong) 國內(nei) 半導體(ti) 設計製造封測銷售額看,半導體(ti) 製造銷售量在三者一直是最低者,12 年以來製造占比雖然有所提高,但依舊在 30 以下。

當前,中國半導體(ti) 產(chan) 業(ye) 正處於(yu) 產(chan) 業(ye) 升級的關(guan) 鍵階段,掌握核心技術是中國半導體(ti) 產(chan) 業(ye) 現階段最重要的目標,國內(nei) 半導體(ti) 製造公司崛起迎來機遇。

1.摩爾定律放緩為(wei) 國內(nei) 製造企業(ye) 提供機會(hui)

上文我們(men) 介紹過摩爾定律的發展,先進製程工藝由於(yu) 需要大量的工藝研發和資本投入,能負擔大額成本投入的晶圓廠越來越少,摩爾定律放緩。除了英特爾、台積電、三星以外,聯電和格芯都宣布了放棄對 7nm 製程的研發。這給國內(nei) 製造企業(ye) 提供了趕超的機會(hui) ,目前中芯國際正在研發 N+1 代製程,華虹半導體(ti) 也在追趕 14nm 製程,以長江存儲(chu) 、合肥長鑫等企業(ye) 深耕存儲(chu) 領域。

2. 產(chan) 業(ye) 鏈轉移,下遊應用細分化也是國內(nei) 半導體(ti) 製造企業(ye) 的一大機會(hui)

伴隨著下遊 PC、智能手機市場的逐漸成熟和飽和,半導體(ti) 行業(ye) 的係統性創業(ye) 機會(hui) 也從(cong) PC、智能手機、服務器三大集中性市場往物聯網、下一代智能終端等碎片化、新興(xing) 化市場轉移,物聯網、新能源汽車等新興(xing) 市場帶來向上重構供應鏈的係統性機會(hui) 。在應用場景方麵,采用先進工藝的芯片種類主要是基帶、CPU、存儲(chu) 等大型邏輯芯片,主要用於(yu) 手機和筆記本電腦,而其他低功耗領域需要一些專(zhuan) 用芯片。對於(yu) 中低端 MCU、電源管理芯片等技術壁壘不高的細分市場,芯片專(zhuan) 用化、性價(jia) 比是重點。以功率半導體(ti) 為(wei) 代表的模擬細分市場中,傳(chuan) 統汽車電子、工業(ye) 級芯片等市場對品控、功耗、性價(jia) 比的要求很高。因此在這些市場,國內(nei) 企業(ye) 可以找到突破口,積極布局滲透市場。例如,三安光電在第三代半導體(ti) 材料 GaN崛起中受益,耐威科技在 MEMS 傳(chuan) 感器研發中持續發展。

3. 終端品牌效應

終端品牌的國產(chan) 化給上遊供應鏈帶來發展機會(hui) ,終端需求向上傳(chuan) 導可以帶動整個(ge) 供應鏈的國產(chan) 化。例如,“蘋果產(chan) 業(ye) 鏈”帶動了台積電、環旭電子和長電科技等企業(ye) 的發展。目前,5G 帶動了“華為(wei) 產(chan) 業(ye) 鏈”的發展,進入華為(wei) 產(chan) 業(ye) 鏈的中芯國際也將在產(chan) 業(ye) 鏈的影響下也會(hui) 有所收益。

4. 政策扶持

根據“中國製造 2025”重點領域技術路線圖對 IC 製造產(chan) 業(ye) 的規劃,國產(chan) 半導體(ti) 製造產(chan) 業(ye) 的發展將圍繞產(chan) 能擴充與(yu) 先進製程同步推進。國家集成電路大基金的投資扶持了半導體(ti) 製造企業(ye) 的發展。

6. 半導體(ti) 製造廠商(略,詳見報告原文)

半導體(ti) 製造廠商主要有台積電、三星、英特爾、聯電、格芯、中芯國際和華虹半導體(ti) 。

……

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們