基於(yu) DSP的嵌入式係統的以太網接口設計一直是熱門領域,目前利用的以太網控製器大多都是ISA接口。隨著PCI總線逐漸取代ISA總線的趨勢,使PCI接口的以太網控製器也成為(wei) PC機的主流,但在嵌入式領域中PCI總線的應用目前並不多見。本文將介紹利用Realtek公司生產(chan) 的具有PCI接口的以太網控製芯片RTL8139實現RTL8139與(yu) DSP接口的方案。

1 RTL8139

RTL8139是帶PCI接口的10M/100M自適應網卡控製芯片,它提供32位PCI總線控製,支持IEEE802.3u 100Base-T和IEEE802.3x的全雙工流量控製;符合PCI 2.2標準,支持高級配置和電源接口(ACPI)和PCI對現代操作係統的電源管理(即對操作係統的直接電源管理),以提高電源管理的效率。此外,RTL8139還支持128KB的Boot ROM,提供網絡喚醒和遠程喚醒功能;含有2個(ge) 2KB的收發FIFO;能夠降低網絡維護成本,消除使用障礙,而且可以很方便地使網絡由10M升級到100M,且帶寬可以達到200Mbps。RTL8139內(nei) 部MAC層結構如圖1所示。

1.1 RTL8139的PCI接口

PCI總線分為(wei) 主(Master)、從(cong) (Target)二種類型,Master可以控製PCI總線,Target不能控製PCI總線。標準的主設備至少有49條線與(yu) PCI總線相連;從(cong) 設備至少有47條線與(yu) PCI總線相連。RTL8139所提供的PCI接口有51條引腳,其引腳簡介如下。

(1)地址/數據信號

AD31~0:地址、數據多路複用的輸入/輸出信號,在FRAMEB有效時,是地址期;在IRDYB和TRDYB同時有效時為(wei) 數據期。

C/BE3~0:總線命令和字節使能多路複用信號,負責傳(chuan) 輸總線命令。在數據期,由傳(chuan) 輸字節使能信號來表示數據線上哪些字節是有效數據。

(2)接口控製信號

FRAMEB:幀周期信號,表示訪問的開始和持續時間。

IRDYB、TRDYB:分別表示主、從(cong) 設備準備好信號,二者必須配合使用,同時有效時方能進行數據傳(chuan) 輸。

STOPB:目標設備請求停止數據傳(chuan) 輸信號。

IDSEL:初始化設備選擇信號,在參數配置讀寫(xie) 傳(chuan) 輸期間,用作片選信號。

DEVSELB:設備選擇信號。

(3)仲裁信號

REQB:總線占用請求信號,表示RTL8139申請總線控製權。

GNTB:總線占用允許信號,表示總線控製權已經交給RTL8139。

主設備都必須有以上2種信號。

(4)錯誤報告信號

PERRB:數據奇偶校驗錯誤信號。

SERRB:係統錯誤信號。

(5)其他信號

CLK:時鍾信號,最高可達33MHz。

CLKRUNB:時鍾運行信號,這是RTL8139增設的信號,用來請求時鍾開始和表示時鍾狀態。

RSTB:複位信號,低電平有效,至少需要120ns的寬度。

INTAB:中斷請求信號,它需要與(yu) RTL8139的ISR和IMR寄存器配合使用。

在嵌入式係統中並不需要連接所有的引腳,可根據係統的實際需要進行選擇。

1.2 主要寄存器

RTL8139的寄存器映射到I/O空間,I/O空間有256個(ge) 地址,地址偏移量為(wei) 00H~FFH。下麵介紹幾個(ge) 比較重要的寄存器。

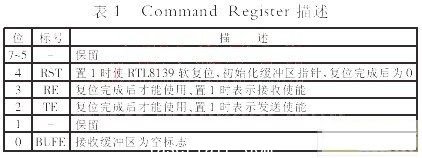

(1)Command Register

該寄存器地址偏移量為(wei) 0037H,功能為(wei) 軟複位網卡,使能網卡的發送和接收。其描述如表1所示。

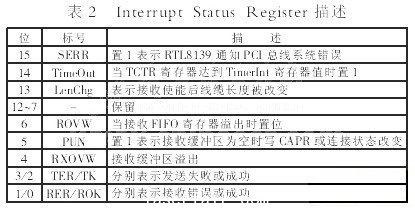

(2)Interrupt Status Register

該寄存器地址偏移量為(wei) 3EH~3FH,在INTA引腳有效時表示中斷源,與(yu) IMR寄存器配合使用,它的值影響當前所有中斷。其描述如表2所示。

(3)Receive Status Register

該寄存器通常可以從(cong) 數據包的包頭中讀出,是RTL8139芯片特有的。通過它可以知道網卡收包的狀態以便進行接收處理。其描述如表3所示。

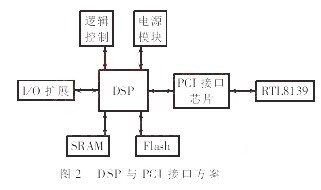

2 係統設計方案

根據RTL8139的以上特點,作者設計了RTL8139與(yu) DSP之間的接口解決(jue) 方案。目前DSP與(yu) PCI的接口一般有二種方案:(1)用CPLD來實現。優(you) 點是可以進行功能優(you) 化,不必實現所有PCI協議的功能,節約係統資源。占用係統資源大的用戶可以做成ASIC,有利於(yu) 降低成本。但由於(yu) PCI協議的複雜性,短期內(nei) 還難以做到操作穩定。(2)用專(zhuan) 門的PCI橋芯片。PCI芯片功能強大,可減少開發時間和成本並能獲得較好的傳(chuan) 輸特性。目前市場上有許多PCI橋芯片產(chan) 品,最為(wei) 常見的是AMCC、PLX、CYPRESS等公司的產(chan) 品,作者選用PLX公司的PCI9054作為(wei) 本係統的PCI接口芯片。DSP與(yu) PCI接口設計方案如圖2所示。

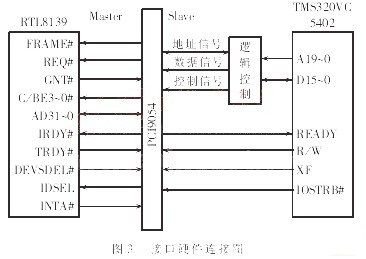

DSP選用TI公司的TMS320VC5402,它的運算速度達100MIps,硬件接口功能強大(具有串行口、HPI主機接口和DMA控製器等),而且價(jia) 格低廉,具有很高的性價(jia) 比。接口的硬件連接如圖3所示。#p#分頁標題#e#

圖3中,DSP通過PCI9054來讀寫(xie) PCI內(nei) 存,地址空間由PCI的基地址開始。PCI9054作為(wei) DSP的從(cong) 設備和RTL8139的主設備。當PCI寫(xie) 時,接收寫(xie) 信號,返回ready信號直到寫(xie) FIFO滿為(wei) 止,並保持ready信號到寫(xie) FIFO可用。當PCI9054從(cong) RTL8139讀出數據時將保持ready信號,直到BALST信號(表示PCI總線上的最後傳(chuan) 輸)有效,讀周期被終止,沒有讀出的數據將被FIFO舍棄。

要使嵌入式DSP係統要獨立運行,必須外接EPROM或Flash存儲(chu) 器用於(yu) 存放程序。與(yu) EPROM相比,Flash芯片功耗低,支持在工作電壓下的擦寫(xie) ,可以方便地編寫(xie) 自己的Flash芯片燒錄程序,通過在片方式完成對Flash芯片的寫(xie) 操作。本設計采用的是SST公司生產(chan) 的SST39VF400A,它是一款基於(yu) CMOS技術的高性能、多用途的Flash存儲(chu) 芯片,其存儲(chu) 容量達4Mb,功耗低,使用2.7~3.3V單電源供電。為(wei) 了方便程序的調試,外接了1片64K×16b的SRAM,以用於(yu) 存放發送數據和接收數據,以便於(yu) 對比,及時地發現數據傳(chuan) 輸的正確性。邏輯控製部分主要用於(yu) 主處理器對外設(如PCI橋芯片、網絡適配芯片、SRAM及Flash等)的讀寫(xie) 控製及地址分配。

3 軟件設計

軟件設計主要分為(wei) PCI網橋和網絡接口二部分。PCI網橋部分主要是對PCI9054進行初始化,即對它的PCI端配置寄存器和本地端配置寄存器進行正確的編程配置,以實現DSP與(yu) PCI網卡的無縫連接。網絡接口部分的編程包括對RTL8139進行複位初始化,數據包的接收和發送。

RTL8139已經實現了OSI中的物理層和數據鏈路層的功能,隻需再加上高層協議即可。作為(wei) 一個(ge) 嵌入式係統,為(wei) 了節省係統資源,需要盡量使用簡化的協議。因此IP地址和本機物理地址在初始化RTL8139時設定,采用本地管理的地址方式,上層協議進行了簡化,沒有封裝複雜的TCP協議。

簡化的網卡初始化程序如下:

#define CMD_RST 0x10 //複位標誌

#define CMD_RE 0x08 //接收使能

#define CMD_TE 0x04 //發送使能

#define SUCCESS 0xFF //網卡初始化成功標誌

Reset_init_rtl8139()

{

CMD=0x10;//軟複位網卡

while((read_cmd & CMD_RST)==0) read_cmd=CMD;

//檢查網卡是否複位完成

write_mac_ip(); //設定網卡的MAC地址和IP地址

CMD=CMD_RE | CMD_TE; //接收發送使能

set_RxConfig(); //接收配置

set_TxConfig(); //發送配置

init_rx_addr(); //初始化接收緩衝(chong) 區地址

Rxmissed=0; //clear 0

CMD=CMD_RE | CMD_TE;

return SUCCESS;

}

程序中:CMD為(wei) RTL8139的Command寄存器,通過它來對芯片複位並檢查複位成功與(yu) 否;write_mac_ip()是向IDR0~IDR5寫(xie) 入MAC地址,設定IP地址;set_RxConfig()主要是對Receive Configuration Register進行設置。此外,網卡初始化程序設定隻接收物理地址匹配的包,不接收組播和廣播。

RTL8139接收緩衝(chong) 區的大小可選,並設定為(wei) 16KB。初始化過程中根據DSP的快慢還需要加一些延時,這一點非常重要。因為(wei) 許多寄存器的設置都需要時間,若時間不夠,某些寄存器的值可能會(hui) 設置不正確,從(cong) 而導致初始化失敗,RTL8139的收發功能也會(hui) 受到影響。

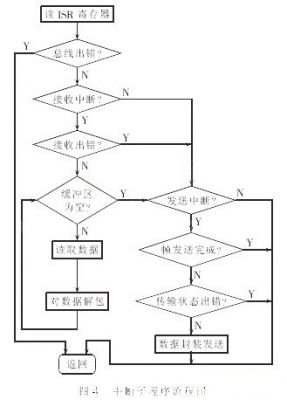

RTL8139數據的收發用中斷方式完成。當主處理器要向網上發送數據時,先將1幀數據通過DMA通道送到控製器的發送緩衝(chong) 區,然後發出傳(chuan) 送命令,RTL8139按照PCI總線主模式將數據從(cong) 發送緩衝(chong) 區轉移到內(nei) 部發送FIFO中。當FIFO中數據包完整時,RTL8139即開始包發送。控製器在數據發送完成後通過中斷方式通知主處理器;接收數據時,網上來的數據包首先被放在接收FIFO中,同時RTL8139要進行組播地址過濾。當接收FIFO中數據包已達到接收配置寄存器的要求時,RTL8139請求PCI總線按照PCI主模式將數據傳(chuan) 到接收緩衝(chong) 區,接收滿1幀後,同樣以中斷方式通知主處理器。數據的收發是通過 DMA通道來完成的。中斷子程序流程圖如圖4所示。

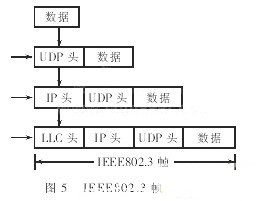

數據包的封裝按照IEEE802.3協議、IP協議和UDP協議,其幀格式如圖5所示。

封裝的過程依次在源數據前加上UDP頭、IP頭和LLC頭。LLC頭即通常所說的以太網包頭,但也可以根據自己的需要加上其他協議如TCP、ARP或HTTP。不過在嵌入式係統中,為(wei) 了節省資源,應盡量減少協議的使用。在分組語音數據傳(chuan) 輸中,實時語音數據可以用UDP,而控製信號可以用TCP。

4 結束語

本文所提出的DSP與(yu) RTL8139的接口解決(jue) 方案已在試驗中得到實現,並已用於(yu) IP分組語音數據的以太網傳(chuan) 輸,效果良好。隨著ISA總線的淘汰,PCI接口的網絡控製器必將在嵌入式領域中得到更廣泛的應用。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們