引 言

現今數控技術的發展方向是開放式體(ti) 係結構的數控係統,但是未來的開放式數控技術發展的主流是基於(yu) 計算機標準總線的“PC+運動控製卡”結構。此類數控係統通常選用高速DSP作為(wei) 運動控製卡CPU,采用主從(cong) 式控製策略,利用PC和DSP都讀取內(nei) 存的方式來實現上/下位機的通信;優(you) 點:信息處理能力強、開放程度高、運動軌跡控製準確、通用性好等特點,被廣泛應用於(yu) 製造業(ye) 自動化控製各個(ge) 領域。

1 硬件電路總體(ti) 設計

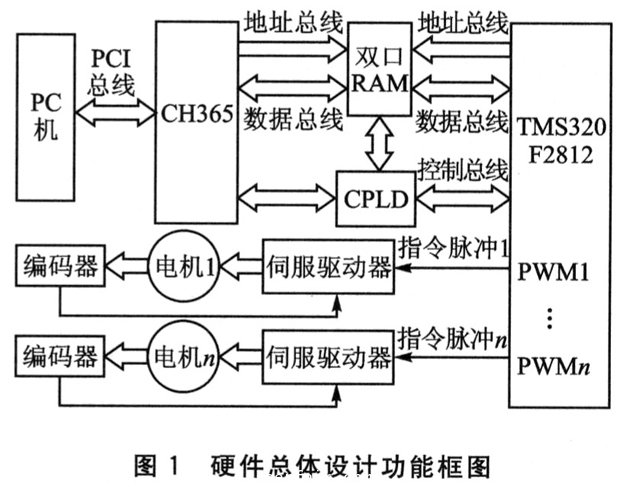

為(wei) 實現對多電機的半閉環控製提供了一個(ge) 良好的開發平台。本項目是設計一款基於(yu) PCI總線的,以DSP芯片TMS320F2812為(wei) 核心的多軸運動控製卡。將PC機的信息處理能力和開放式的特點與(yu) 運動控製器的運動軌跡控製能力有機地結合在一起,利用雙口RAM作為(wei) 公共存儲(chu) 單元實現上/下位機的通信。

係統硬件總體(ti) 設計功能框圖如圖1所示。

2 雙口RAM接口電路設計

2.1 雙口RAM與(yu) DSP和CH365的連接

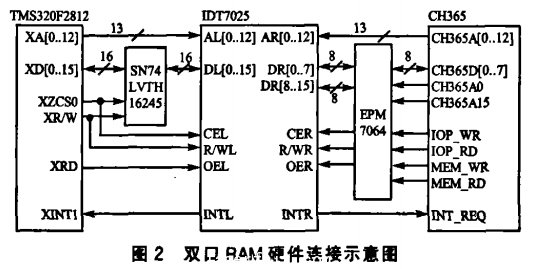

本係統選用雙口RAM芯片IDT7025作為(wei) DSP與(yu) CH365雙向通信的緩衝(chong) 芯片。IDT7025芯片是一款高速的8K×16位雙口靜態RAM,它提供2個(ge) 獨立的端口,允許兩(liang) 個(ge) (左、右)端口同時讀/寫(xie) 數據,每個(ge) 端口具有自己獨立的控製信號線、地址線和數據線,可高速存取數據,可與(yu) 大多數高速處理器配合使用,而無需插入等待狀態。

雙口RAM允許2個(ge) CPU同時讀取任何存儲(chu) 單元(包括同時讀同一地址單元),但不允許同時寫(xie) 或一讀一寫(xie) 同一地址單元。本係統采用基於(yu) 郵箱機製的INT中斷法處理雙口RAMD地址競爭(zheng) 衝(chong) 突現象,避免由此而產(chan) 生的讀/寫(xie) 錯誤。

下麵簡要介紹一下IDT7025中斷的原理:當用戶要用到中斷功能時,內(nei) 存中的1FFE和1FFF單元將作為(wei) 中斷標誌郵箱傳(chuan) 遞命令信息。當左端口定義(yi) 為(wei) 寫(xie) 狀態(CEL=R/WL=VIL),且在內(nei) 存1FFF中進行寫(xie) 操作時,右端口的中斷標誌INTR為(wei) 低電平,可以向右端口發出中斷請求;當右端口對地址1FFF進行訪問時(CER=OER=VIL),無論讀寫(xie) 都可以清除右端口中斷標誌INTR。相反也是一樣的,當右端口對內(nei) 存1FFE進行寫(xie) 操作時,左端口可以發出中斷請求;當左端口訪問地址1FFE時,清除左端口中斷標誌。使用中斷時,向1FFF和1FFE寫(xie) 的內(nei) 容由用戶自行定義(yi) ,本係統中設定:申請中斷時向郵箱寫(xie) 入1或其他大於(yu) 0的整數,清除中斷時向郵箱寫(xie) 入0。

2.2 數據總線擴展電路設計

係統采用了雙口RAM作為(wei) DSP和CH365之間數據傳(chuan) 輸的緩衝(chong) 芯片,而TMS320F2812的地址總線為(wei) 19位,IDT7025為(wei) 13位,CH365為(wei) 16位,因此,把IDT7025的13位地址線A[O..12]分別與(yu) DSP的地址線XA[O..12]和CH365的地址線A[O..12]相連,並將CH365的地址線A0用作數據總線擴展的使能信號。

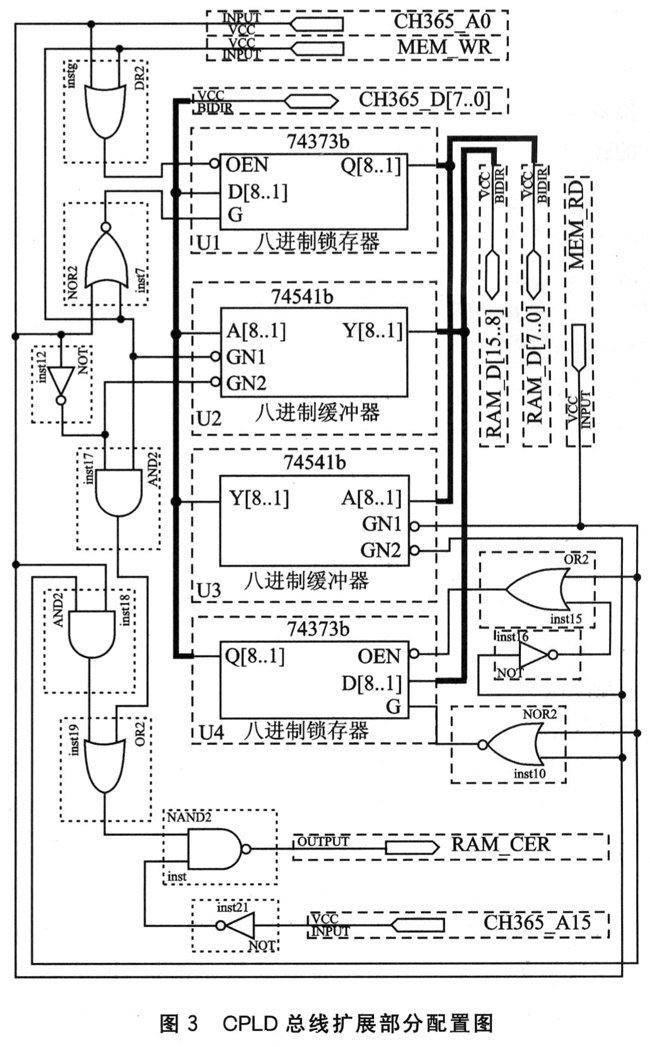

CPLD芯片選用A1tera公司生產(chan) 的EPM7064,通過CH365地址線A0的使能對16位數據進行分時讀/寫(xie) ,從(cong) 而解決(jue) 了數據總線的擴展問題。其內(nei) 部邏輯電路如圖3所示,其中主要包括2個(ge) 鎖存器(74373b),和2個(ge) 三態門緩衝(chong) 器(74541b)。

在本係統中,CH365向雙口RAM寫(xie) 入數據時,首先CH365_A0為(wei) 低電平,鎖存器U1使能信號G高電平有效,三態門U2無效(GN2為(wei) 高電平),低8位寫(xie) 入鎖存器;然後偏移地址加1,CH365_A0為(wei) 高電平,三態門U2使能信號有效,高8位數據直接寫(xie) 入雙口RAM,同時低8位數據通過鎖存器U1寫(xie) 入雙口RAM(OEN為(wei) 低電平)。CH365讀取雙口RAM數據時,首先CH365_A0為(wei) 低電平,低8位數據通過三態門U3直接讀入到CH365中,高8位數據鎖存到鎖存器U4中;然後偏移地址自動加1,CH365_A0為(wei) 高電平,高8位數據由鎖存器U4讀入CH365。

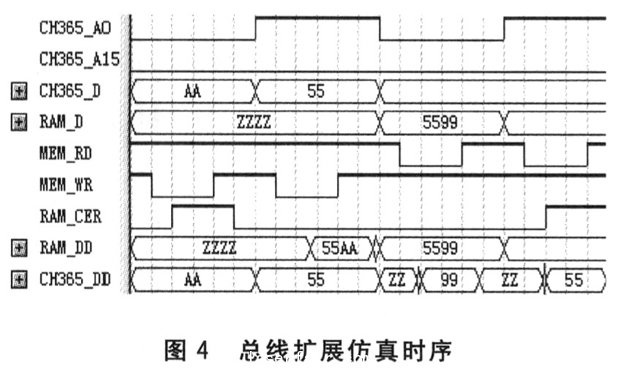

對上述邏輯關(guan) 係用“MAX+PLUS”進行仿真後,得到圖4所示的時序。圖中RAM_DD和CH365_DD表示仿真結果,從(cong) 圖中可知仿真結果完全符合設計要求。

3 上/下位機通信軟件設計

在硬件電路實現之後,把完成的板卡插於(yu) PC機的PCI插槽,上電後根據係統提示安裝CH365驅動程序,在正確安裝好硬件之後,利用API函數,就可以在VC環境下編寫(xie) 和調試PCI和DSP的通信軟件了。

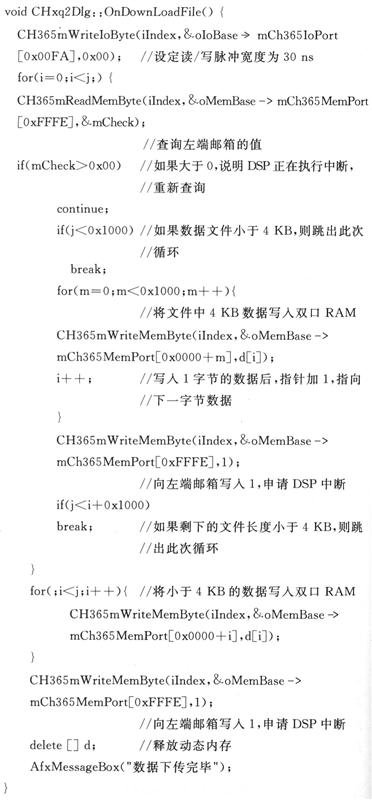

由上述可知,雙口RAM的高4 KB空間用於(yu) PC機向DSP下載數據,如果數據大於(yu) 4 KB,則存在著一次不能夠把全部數據下載到DSP中的問題。因此,采取了向雙口RAM中循環寫(xie) 入數據的辦法,即PC機向雙口RAM一次隻寫(xie) 入4 KB數據,接著向DSP申請中斷。DSP響應中斷一次性將4 KB數據複製到DSP其他大容量存儲(chu) 空間(如擴展SRAM)中,然後釋放雙口RAM空間。此時PC機便可再寫(xie) 入4 KB數據,如此循環往複,直到將所有數據都寫(xie) 入DSP中。部分代碼如下:

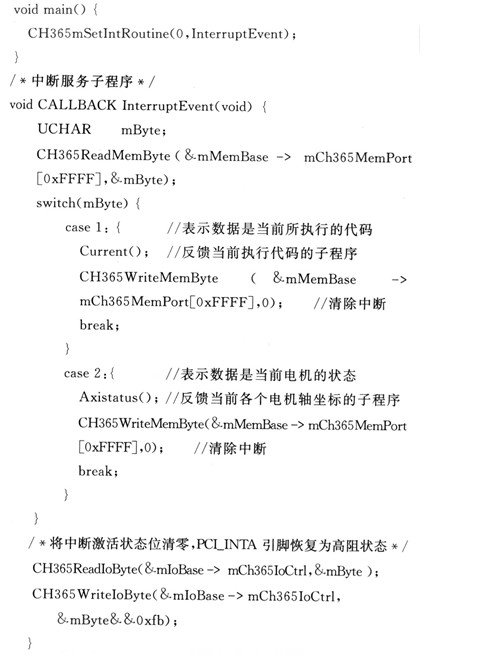

數據反饋功能主要是通過CH365響應DSP中斷來實現的。DSP程序將數據寫(xie) 入雙口RAM低4 KB空間後向CH365申請中斷,CH365響應中斷將數據反饋到PC並顯示到人機界麵。中斷函數部分代碼如下:

結 語

隨著計算機技術和電子技術的發展,將運算高速、功能強大的數字信號處理器應用於(yu) 運動控製,可以實現複雜的控製算法和實現高精度、高速度、多軸聯動,在數控應用中,將會(hui) 占據越來越重要的地位。而快速準確的通信又是這種運動控製器的基礎。本文介紹的通信方式,具有性能可靠,硬件結構簡單,價(jia) 格便宜的優(you) 點,具有較好的應用前景。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們